一種基于FPGA的線陣CCD瞬態光譜信息采集系統設計

系統結構

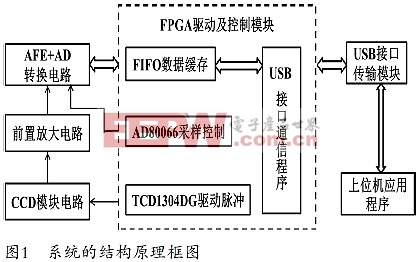

本文引用地址:http://www.j9360.com/article/142474.htm系統的結構原理框圖,如圖1所示。系統主要包括CCD數據采集模塊電路、輸出信號前置放大電路、帶模擬前端的AD轉換電路、FPGA驅動及控制電路和USB接口電路等五部分。

系統上電后,上位機程序通過USB設備向FPGA發送控制命令,USB設備在該命令控制下完成對FPGA數據采集參數的初始化設置。FPGA根據初始化后的采集參數,產生相對應的TCD1304DG驅動時序,使之在該驅動時序的嚴格控制下工作。CCD采集模塊輸出的模擬信號經過前置放大電路處理后,進入專用視頻信號處理器AD80066完成模擬前端處理和A/D數據轉換,由FPGA片上高速FIFO實現數據緩存,然后通過USB接口將數據從FIFO中讀出,傳輸給上位機以進行后期數據分析和處理。

系統的硬件構成

FPGA驅動及控制模塊

本系統采用Xilinx公司Spartan-3系列的XC3S1000芯片,它具有很高性價比和豐富的邏輯資源,能滿足采集系統的要求。FPGA作為該數據采集系統的控制核心,主要用來產生TCD1304DG的驅動時序、控制AD80066完成數據采樣、合理配置內部FIFO用于緩存數據、通過USB接口通信模塊將數據正確地傳輸到上位機中。

CCD模塊電路

系統采用TCD1304DG作為感光元件,它是一款高靈敏度、低暗電流噪聲、寬動態范圍的線陣CCD器件。內部集成有驅動電路、采樣保持電路,尤其是電子快門功能更便于探測爆轟之類的瞬時事件。TCD1304DG傳感器工作時需要3路驅動時鐘,包括轉移脈沖SH、光積分控制脈沖 ICG 和主時鐘脈沖M。通過對TCD1304DG的時序分析,在本設計中采用Verilog HDL語言進行編程,以完成TCD1304DG的驅動時序脈沖設計。

由于光積分時間的長短與CCD器件輸出信號的強弱有關,選擇合適的光積分時間將關系到CCD輸出信號的質量。因此,本設計中采用了在FPGA內部控制線陣CCD光積分時間,實現曝光時間的自動控制。啟動CCD的電子快門功能調節時,最小的曝光時間將達到10ms。

模擬信號相關文章:什么是模擬信號

fpga相關文章:fpga是什么

脈沖點火器相關文章:脈沖點火器原理

評論