基于PC/104總線的雷達數據采集板設計

摘要:介紹了一種基于PC/104總線的雷達數據采集板的設計。硬件上采用CPLD進行邏輯控制,簡化了硬件電路。該采集板具有精度高、成本低等優點,為雷達測試設備的數據采集提供了一套可行的硬件設計方案。

本文引用地址:http://www.j9360.com/article/132644.htm引言

隨著現代雷達功能多樣化、復雜化,要求研制和裝備的周期越來越短,為保障裝備部隊的雷達系統充分發揮出優越的性能,雷達測試設備的作用顯得非常重要。本文提出了一種適用于雷達測試設備的數據采集板設計方案,能夠有效地對I/Q模擬基帶信號進行數據采集和處理,并能滿足雷達測試設備小型化的要求。

數據采集板組成及設計原理

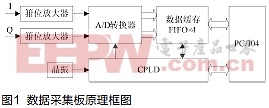

數據采集板由A/D轉換電路、數據FIFO緩存電路、CPLD、PC/104 CPU模塊等四部分組成,其原理框圖如圖1所示。

A/D轉換電路

在本設計中,A/D轉換器選用ADI公司生產的12位高速模數轉換器AD10242。它是一種全雙工、帶有模擬輸入信號調節的A/D轉換器,集成了放大器、基準電壓源、模數轉換器和輸出緩沖器,其采樣速率可達40MSPS,采樣延遲為1ns。由于雷達模擬基帶信號電壓變化范圍較寬,而AD10242的輸入電壓只有三檔可調:±0.5V、±1.0V、±2.0V,因此為了減小轉換誤差,使模擬信號在A/D轉換器輸入的允許范圍內盡可能大,就需要對模擬信號的幅值進行必要的調整,即在信號進行模數轉換之前對信號進行濾波和降壓等信號調理,使其電壓符合A/D轉換器的要求。本設計中,I/Q模擬基帶信號通過2片ADI公司的箝位放大器AD8036,使其信號電壓箝位在±1.0V以內。

數據FIFO緩存電路

I/Q模擬基帶信號經A/D轉換后變為2路12位數字信號,分別連接至2片IDT7203的輸入數據總線上。IDT7203是IDT公司生產的高性能FIFO芯片,該芯片是一個雙端口的存儲緩沖芯片,具有2k×9位的RAM陣列,結構簡單,易于操作,其內部的讀、寫指針可在先入先出的基礎上對數據自動寫入和讀出。IDT7203通過外部電路提供的寫信號WR和讀信號RD進行數據的讀寫操作,并提供了三種標志位:全滿標志位FF、半滿標志位XO/HF和全空標志位EF來標明數據的寫入情況,以防止數據的空讀和溢出。在本數據采集板中,4片FIFO緩存器均工作在單一器件模式下,用來存儲I路和Q路模擬基帶信號從啟動A/D轉換到PC/104總線讀取數據的時間內經A/D所轉換的數據。在實際使用時,可以通過PC/104軟件編程設定FIFO的使用深度,這樣可以大大減少A/D轉換的中斷次數,保證較高的采樣頻率和較低的中斷頻率。

評論