針對未來十年 “All Programmable”器件的顛覆之作

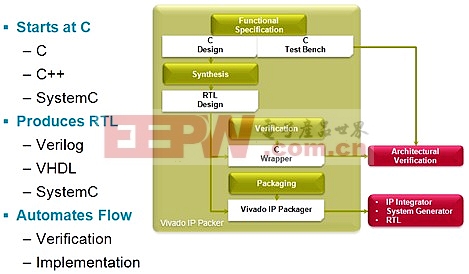

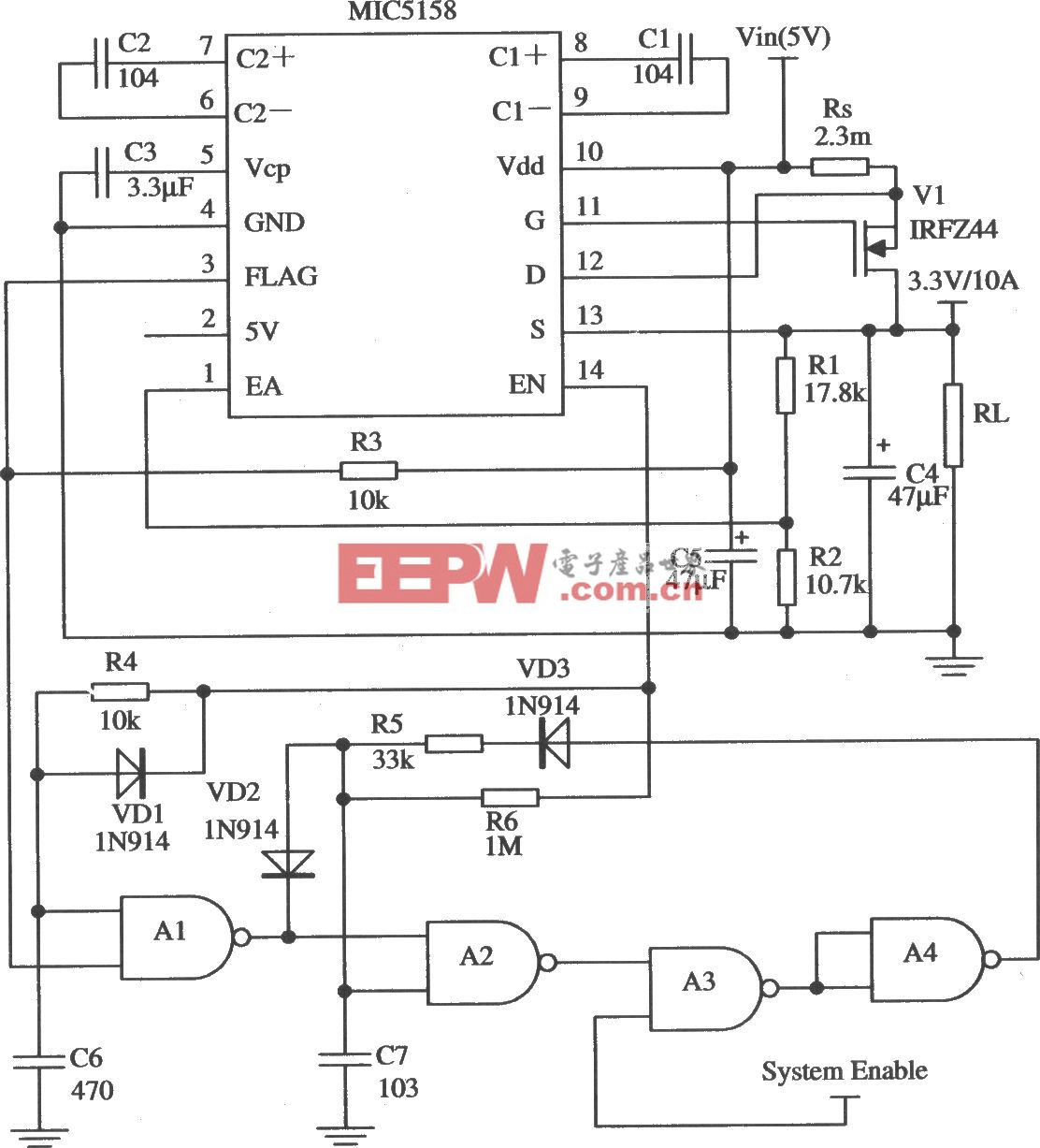

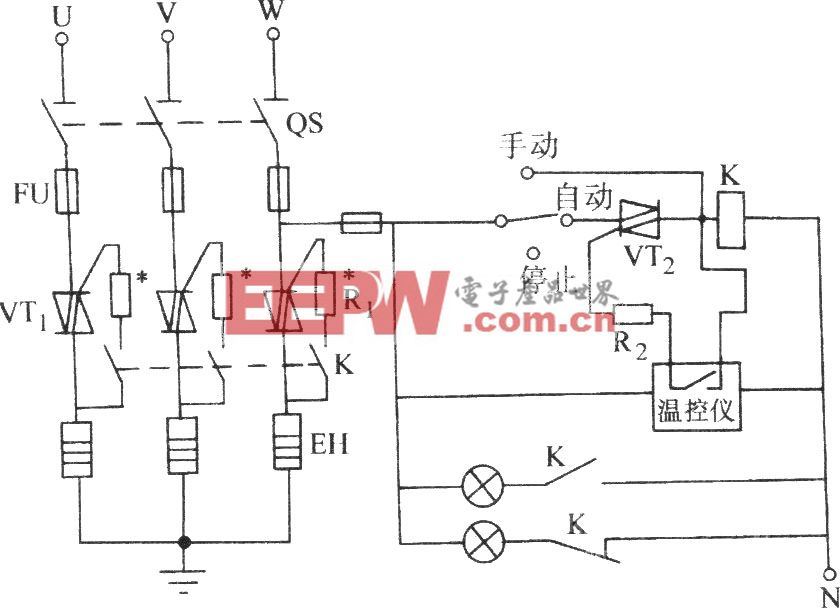

在這個流程中,用戶先創建一個設計 C、C++ 或 SystemC 表達式,以及一個用于描述期望的設計行為的 C 測試平臺。隨后用 GCC/G++或 Visual C++ 仿真器驗證設計的系統行為。一旦行為設計運行良好,對應的測試臺的問題全部解決,就可以通過 Vivado HLS Synthesis 運行設計,生成 RTL 設計,代碼可以是 Verilog,也可以是 VHDL。有了 RTL 后,隨即可以執行設計的 Verilog 或 VHDL 仿真,或使用工具的 C封裝器技術創建 SystemC 版本。然后可以進行System C架構級仿真,進一步根據之前創建的 C 測試平臺,驗證設計的架構行為和功能。

本文引用地址:http://www.j9360.com/article/131872.htm設計固化后,就可以通過 Vivado 設計套件的物理實現流程來運行設計,將設計編程到器件上,在硬件中運行和/或使用 IP 封裝器將設計轉為可重用的 IP。隨后使用 IP 集成器將 IP 集成到設計中,或在系統生成器 (System Generator) 中運行 IP。

圖三 – Vivado HLS 支持設計團隊直接從系統級開始他們的設計.

這只是使用該工具的方法之一。實際上在即將發行的賽靈思Xcell雜志中,安捷倫的 Nathan Jachimiec 和賽靈思的 Fernando Marinez Vallina 將介紹如何使用 Vivado HLS 技術(在 ISE設計套件的流程中稱為 AutoESL 技術)為安捷倫開發 UDP 包引擎。

VIVADO 仿真器

除了 Vivado HLS,公司還為該套件新開發了一種同時支持 Verilog 和 VHDL 的混合語言仿真器。Feist 表示,只需要單擊鼠標,用戶就可以啟動行為仿真,然后從集成波形查看器中查看結果。通過采用最新性能優化的仿真內核,可加速行為級仿真速度,執行速度比賽靈思 ISE 設計套件仿真器快三倍。采用硬件協仿真,門級仿真速度則可加快 100 倍。

評論