Altera全新Qsys工具加速FPGA產品上市步伐

在FPGA設計領域目前存在著三大主要難題:設計規模擴大、設計重用、設計驗證時間太長。這三大難題嚴重影響著FPGA設計的效能,將減緩產品由研發到上市的時間,是亟需解決的重點問題。

本文引用地址:http://www.j9360.com/article/130918.htm2012年3月30日,“Altera亞太區采用Qsys實現系統集成研討會•北京站”在清華大學舉行,該活動重點介紹了Altera新的系統集成工具Qsys,及其如何通過Qsys提高設計效能。

簡化設計過程

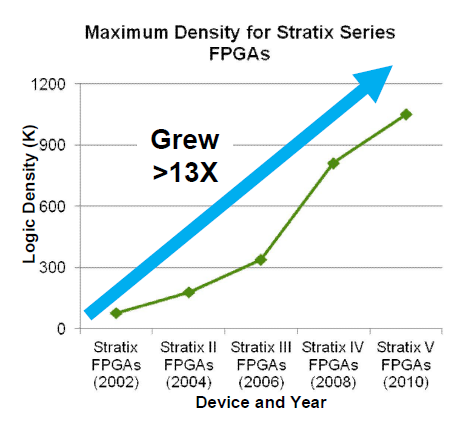

隨著半導體技術的不斷發展,由于半導體工藝的不斷提升,器件的集成度也隨之提升,FPGA器件的邏輯密度也急劇增加,因此使得設計開發的規模不斷擴大,復雜度上升。目前,FPGA 器件密度已經提高到百萬邏輯單元(LE),因此,設計團隊需要實現更大更復雜的系統,在更短的時間內滿足越來越高的性能需求,傳統的設計模式顯然已經跟不上硬件的發展速度。

圖1 Altera Stratix系列FPGA邏輯密度增長

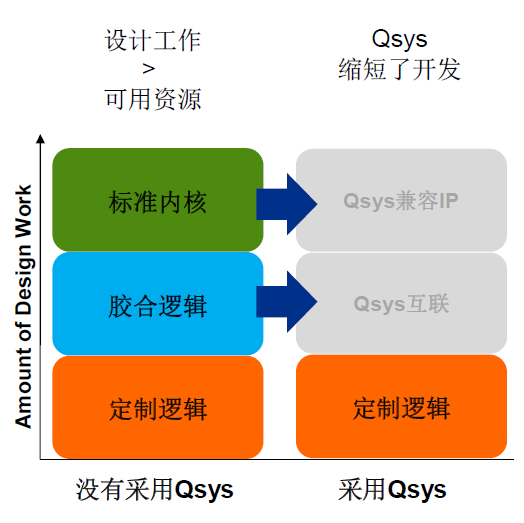

FPGA設計工作主要包含三個部分:標準內核、膠合邏輯和定制邏輯。標準內核部分一般采用相應的標準IP進行設計,膠合邏輯部分主要是實現FPGA內部各部分(標準內核、存儲器、定制邏輯等)間的互聯,定制邏輯則是設計者自主開發實現差異化的部分。Qsys采用的是系統級開發,通過片上網絡架構,可以大幅簡化設計工作,提高設計效能。Qsys包含多種兼容IP,如PCIe、DDR3、JTAG、UART等,可以把標準內核部分的工作降至最低。Qsys能夠自動完成部分諸如接口協議、存儲器等相關的繁瑣且容易出錯的集成任務,極大地提高了設計效率。這樣,Qsys使得設計者可以把大部分的精力都放在定制邏輯部分。

圖2

提升設計重用

當前半導體行業內人才流動是很大的,現任工程師和將來的工程師想要重復使用前任工程師曾經開發的設計,難度是很大的。在設計重用的過程中常常會出現以下問題:工程師需要對接口進行重新設計;工程師需要為各種修改后的設計提供支持;缺少相應的文檔,使得其它工程師無法得知接口是如何工作的。

圖3 Altera公司亞太區產品市場經理謝曉東

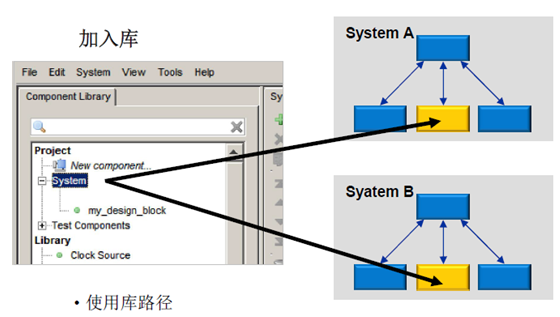

據Altera公司亞太區產品市場經理謝曉東先生介紹,Qsys是業內首個提供子系統設計重用的FPGA開發工具。Qsys增強了設計重用功能,提供標準接口如Avalon、AXI3、AXI4等,使得設計者不需要重新設計接口。Qsys提供了組件編輯器來讓用戶增強RTL設計,同時,Qsys還可以自動封裝和改進用戶的設計,讓用戶可以將自己的設計打包為獨立IP,并且首次做到將子系統打包,極大地方便了日后設計重用和共享。

圖4 Qsys打包設計便于重復使用

加速設計驗證

在設計完成之后,通常需要花費大量的時間對設計進行驗證以確保設計的正確性,這一過程常常超過了設計本身所花費的時間。特別是隨著設計規模的不斷擴大,驗證的復雜度和難度也迅速膨脹。

通過提取/探測100/1000寄存器的方式進行驗證將花費大量的時間,而Qsys采用了通過讀寫操作的方式進行驗證,如圖所示,通過對地址位置進行讀寫操作,先確定出現問題的模塊,再針對出現問題的模塊進行更細化的驗證。以這種方式可減少證流程,縮短驗證設計所需的時間,加快產品上市的步伐。

圖5 Qsys同過讀寫操作進行設計的驗證

評論