基于Spartan-6的多路網(wǎng)絡數(shù)據(jù)采集卡設計與實現(xiàn)

引言

本文引用地址:http://www.j9360.com/article/127893.htm隨著互聯(lián)網(wǎng)的迅猛發(fā)展,網(wǎng)絡監(jiān)控的需求日益迫切。為了實現(xiàn)對網(wǎng)絡實時監(jiān)控,有必要及時全面地收集、分析網(wǎng)絡的數(shù)據(jù),準確獲取網(wǎng)絡信息,對網(wǎng)絡的信息進行監(jiān)控,及時發(fā)現(xiàn)可能會出現(xiàn)的問題。然而隨著網(wǎng)絡帶寬的增加和規(guī)模的擴大,大規(guī)模網(wǎng)絡數(shù)據(jù)采集面臨著數(shù)據(jù)規(guī)模龐大和數(shù)據(jù)到達速度過快的挑戰(zhàn)。為了克服上述困難,通常采用硬件實現(xiàn)完成數(shù)據(jù)采集功能。

隨著FPGA的發(fā)展,其內部資料日益豐富,速度和性能大大提高,特別是內部嵌入了大量IP核,使得FPGA上進行高速網(wǎng)絡數(shù)據(jù)采集成為可能。本文涉及的多路網(wǎng)絡采集卡系統(tǒng)采用Xilinx的Spartan 6系列中XC6SLX45T FPGA,獲取8路10/100M RJ45端口送來的網(wǎng)絡數(shù)據(jù)包,并將數(shù)據(jù)包發(fā)送到PC機進行分析和監(jiān)控,最終根據(jù)分析結果來判斷網(wǎng)絡中的異常情況。

系統(tǒng)概述

系統(tǒng)框圖

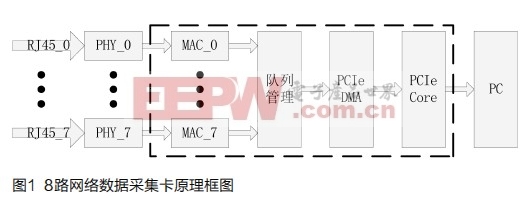

圖1所示為系統(tǒng)的原理框圖。8路10/100M網(wǎng)絡數(shù)據(jù)通過RJ45接口送入到PHY芯片,PHY芯片完成轉換之后,通過MII接口送到FPGA。FPGA中集成了8路MAC核,將網(wǎng)絡數(shù)據(jù)輸出到隊列管理;隊列管理對每路MAC的數(shù)據(jù)包進行管理,并輸出到PCIe的DMA模塊;DMA模塊將數(shù)據(jù)包發(fā)送到PCIe硬核,直接寫入到PC機的內存,以便PC機進行分析。

隊列管理

由于網(wǎng)絡數(shù)據(jù)的包大小不同,在一個包沒有讀完之前有可能第二個包到來,因此有必要對網(wǎng)絡的數(shù)據(jù)包進行隊列管理,避免數(shù)據(jù)包丟失的情況。

本系統(tǒng)中的隊列管理采用雙口RAM和FIFO聯(lián)合構成,其中雙口RAM用來存儲數(shù)據(jù)包,F(xiàn)IFO用來存儲數(shù)據(jù)包的起始地址和結束地址。當FIFO有數(shù)據(jù)時說明RAM中有數(shù)據(jù)包,如果此時并沒有數(shù)據(jù)包在向DMA中寫數(shù)據(jù),那么就可以讀出當前數(shù)據(jù)包寫入到DMA模塊;如果此時正在向DMA模塊寫數(shù)據(jù),則等待寫完后再讀下一個包。

由于網(wǎng)絡數(shù)據(jù)和PCIe DMA模塊的時鐘處于兩個時鐘域,所以采用雙口RAM和FIFO也可以起到數(shù)據(jù)同步的作用。

評論