Xilinx FPGA的Fast Startup

在眾多當代應用中,嵌入式系統必須滿足極其苛刻的時序要求。其中之一就是啟動時間——即上電后電子系統進入可操作狀態所需要的時間。PCI Express產品或汽車應用中基于CAN的電子控制單元(ECU)就是具有嚴格時序要求的電子系統的應用實例。

本文引用地址:http://www.j9360.com/article/125814.htm標準PCI Express(PCIe)系統上電后僅100毫秒,系統的根組件就開始掃描總線以便弄清拓撲結構,并在這一過程中進行初始化配置。 如果PCIe設備沒有準備好響應配置請求,根組件就找不到此PCIe設備,并認為它不存在。該設備將無法加入PCIe總線系統。[1]

汽車應用中的情形與此大體相仿。在基于CAN的網絡中,ECU進入睡眠模式,這時它們將停止運行并切斷電源連接。只有很少部分電路仍然保持戒備狀態,以便探測喚醒信號。一旦出現喚醒事件,ECU就會重新連接電源并開始引導。雖然在喚醒事件后的頭一個100 毫秒內允許錯過一些消息,但在此之后所有ECU都必須在網絡(如CAN網絡)上做好充分的運行準備。

Xilinx Automotive、Xilinx研究實驗室以及德國卡爾斯魯厄技術研究所之間合作展開了深入的研發工作,正在設法通過一種FPGA兩步配置方法解決這一問題。

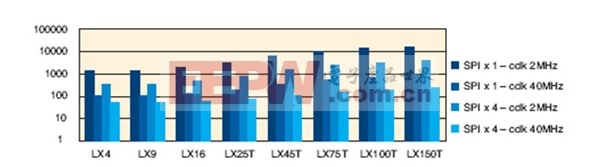

半導體行業的科技趨勢已經能使FPGA廠家大大增加其器件中的資源。但比特流規模也在成比例地增長,配置器件需要的時間也是如此。因此,即使對于中等規模的FPGA,使用低成本配置方案也不可能滿足嚴格的啟動時序要求。圖1表示不同的Xilinx® Spartan®-6 FPGA器件在使用低成本SPI/Quad-SPI配置接口時的配置時間。即使使用快速配置方案(即在40 MHz配置時鐘下運行的Quad-SPI),也只有小型FPGA器件才能達到100 毫秒的啟動時序要求。對于Xilinx Virtex®-6器件來說,這個結果看來更具挑戰性,因為這些器件提供了更豐富的FPGA資源。

為了克服這個難題,Fast Startup分兩步配置FPGA器件,而非單步(整片)的全器件配置。按照這種新穎的思路,我們的策略是在上電時使用最高優先級比特流僅載入時序關鍵模塊,然后再載入非時序關鍵模塊。這種方法最大程度地減少了初始配置數據,從而最大程度地減少了在面向時序關鍵設計的FPGA器件啟動時間。

FAST STARTUP對比部分重配置

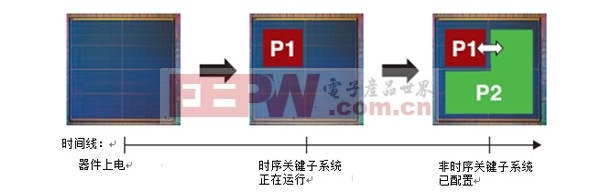

Fast Startup允許FPGA設計盡快啟動設計的關鍵模塊,關鍵模塊的啟動速度比標準全配置方法要快得多[2]。雖然,從本質上來講Fast Startup利用了部分重配置,但它與這種方法的傳統概念所有不同。部分重配置的初衷是將完整設計作為可在運行時修改的初始配置使用。相反,Fast Startup已經使用了一個初始的部分比特流,以在上電時僅僅配置FPGA器件的一個特定(很小的一部分)區域。第一次配置僅包含完整FPGA設計中必須配置和快速運行的那些部分。而剩下的部分則在以后、在運行時,利用部分重配置進行配置。圖2說明了這一順序概念。

工具流程概述

Fast Startup的工具流程依靠設計保存流程,來創建針對時序關鍵子系統及非時序關鍵子系統的部分比特流。

設計保存流程將FPGA設計分割為邏輯模塊(稱為“分區”)。分區構成了層次邊界,將內部模塊與設計中的其他組件相互隔離。分區一旦實現(即完成布局和布線),就能被其他實現運行導入,以按照每個實例中完全相同的方式實現該分區的模塊[3]。

因此,使用Fast Startup方法的第一步是將完整的FPGA設計分成兩部分:即含有時序關鍵子系統的高優先級分區和針對其余組件的低優先級分區。

圖1-計算出的Spartan-6配置時間的對數表示(按最壞情況計算)

圖2 – Fast Startup概念:順序配置

評論