一種高速I2C總線從器件接口IP核的設計與實現

引言

I2C總線作為一種事實上的國際標準,在超過100種不同的IC上實現并且得到超過50家公司的許可。它具有連線少,結構簡單的特點。本文介紹了一種高速I2C從器件接口電路IP核設計。在系統應用中,單片機作為主控器件,本IP核作為從器件中的接口電路,它們通過I2C總線相連,實現MCU對IC或FPGA中相關寄存器的訪問。從而代替了MCU通用的地址數據接口,大大減少了IC或FPGA的管腳數量,節省了I/O資源,這對于I/O資源緊張的IC設計和FPGA開發是非常有意義的。

I2C總線簡介

I2C總線利用兩條線SDA(串行數據線)和SCL(串行時鐘線)完成總線上設備間的數據交換。出現過3個版本標準:1992年的v1.0、1998年的v2.0和2000年的v2.1。I2C總線支持串行的8位雙向數據傳輸,傳輸速率在標準模式下可達100kbit/s,快速模式下可達400kbit/s,高速模式下可達3.4Mbit/s。包含四種工作模式:主機發送模式、主機接收模式、從機接收模式、從機發送模式。

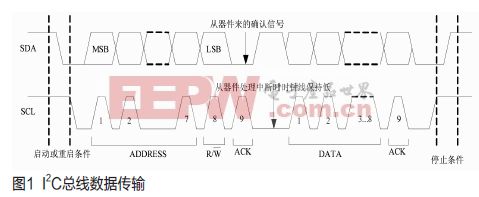

I2C定義了7位和10位兩種從機地址的數據傳輸模式。一般的,7位地址模式應用比較廣泛,其數據傳輸模式如圖1所示。

從圖1中可以看到,當時鐘線SCL=1,數據線SDA從“1”變為“0”時,即表示出現了一個啟動條件(或是重新啟動條件)。其后是7位地址信號,第8位表示的是本次訪問的類型(讀/寫),“0”表示寫,“1”表示讀。第9位是從器件的應答信號,“0”表示應答確認,“1”表示應答不被確認。之后數據以9位循環,前8位是數據第9位是從器件的應答位。當時鐘線SCL=1,數據線SDA從“0”變為“1”時,既表示出現了一個停止條件。啟動條件發生后開始數據傳輸,停止條件發生后表示本次數據傳輸結束。

評論