基于FPGA的高速通道校正實現

前言

當今社會無線通信迅猛發展,無線通信用戶激增,要解決通信系統容量、帶寬限制等這些嚴重問題的一個關鍵技術就是多天線通信技術。這項技術的使用能大幅度地提高無線通信系統的頻譜效率和鏈路可靠性,與單天線系統相比,用多天線系統發射和接收信號能獲得陣列增益(或稱波束形成增益)、分集增益、多路復用增益和干擾抑制等優勢。然而多天線技術帶來諸多優勢的同時會不可避免地引起通道不一致性問題[1]。在實際工程應用中,陣列接收機的多個通道由于PCB(印制電路板)走線長度不等、通道特性存在差異等硬件的非理想因素,導致多個通道接收到的信號存在差異,典型情況為多通道信號存在相位差,通道校正即通過通道校正算法,將多通道信號進行修正,使其差異縮小為一個可接收范圍。

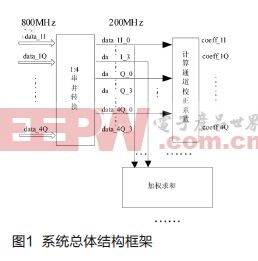

本文在現代通信系統數據傳輸速度極大提高的背景下,提出一種基于Xilinx Virtex-5 FPGA的高速通道校正的實現方案,通過使用可靠的片內高速串并轉換器ISERDES[2-3],將8路800MHz輸入信號轉換為32路200MHz信號,進一步完成通道校正系數計算、加權求和等操作,從而實現800MHz的通道校正實現。

降低信號處理速度方法

由于FPGA內部集成的乘法器、加法器等IP CORE(知識產權核)運算速度最高僅有550MHz[3],在實際應用中為保證運算的穩定性,一般采取低于300MHz的運算速度,要實現速度高達800MHz的運算速度,必須使用降低數據速率的方法。本文中使用賽靈思(Xilinx)公司在其產品Virtex-5中集成的高速串并轉換器(ISERDES),它是為需要高速數據采集等應用開發的專用模塊,能夠提供高速的I/O處理能力,不受FPGA內部資源的限制,不占用系統邏輯資源[2]。通過對ISERDES各參數端口進行配置,使其滿足實際應用,本文實現將800MHz的輸入數據實現1:4串并轉換,并行輸出的數據速率為200MHz。

整個系統結構框圖如圖1所示。系統包括:串并轉換、計算通道校正系數、加權求和三個子模塊構成。

評論