SPI接口與CRC算法在雙DSP數據通信中的應用

摘要:提出了一種基于DSP28335片上SPI模塊和CRC校驗算法的數據通信方案。給出了接口電路設計、SPI模塊驅動程序設計和求取CRC校驗碼的具體步驟,重點介紹了通信協議中從機發送請求機制和錯誤幀重發機制的實現,解決了SPI從機不能發起傳輸的問題,并提高了通信雙方的差錯檢測能力。實驗結果表明,該方案數據傳輸速度快,可靠性高,滿足飛控計算機的性能要求。

本文引用地址:http://www.j9360.com/article/117273.htm關鍵字:SPI;CRC;TMS320F28335;雙核通信;差錯檢測在基于雙DSP架構的某型飛控計算機系統中,兩片DSP分工協作,1片專用于導航信息的解算和傳感器信息的綜合處理,另1片專用于控制律解算和機載任務設備管理。借助雙DSP強大的處理能力和豐富的片上資源,實現了電路結構的簡化和DSP芯片的降額使用,滿足飛控系統高性能、高可靠性的設計要求。

雙DSP的分工協作離不開二者之間高效、可靠的數據通信。本系統最終選用SPI通信方式實現雙DSP間的數據傳輸。

系統概述

系統總體結構

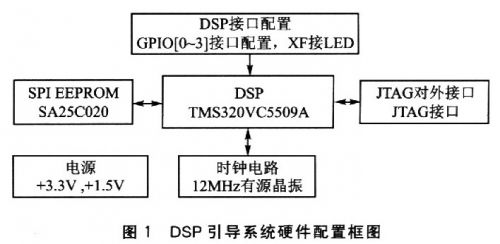

圖1給出了雙DSP架構飛控計算機的結構示意圖。導航DSP完成導航信息的解算和傳感器信息的綜合處理,并將處理結果送至飛控DSP;飛控DSP據此完成控制律解算,并刷新舵面給定信息,實現無人機飛行姿態和航跡的實時調整。導航DSP和飛控DSP還要共同完成機載任務設備和離散量設備的管理,完成飛行任務。雙DSP均選用TI公司面向控制領域的高性能浮點型數字信號處理器TMS320F28335。

TMS320F28335片上SPI模塊遵循標準的SPI通信協議[3],并具如下增強特性:有4種時鐘模式可供選擇,兼容各種不同時序特性的SPI設備;通信波特率有125種設置方案可供選擇,在DSP全速工作時,速率達10Mbits/s以上;發送和接收均有16級FIFO可用,能夠實現16字數據的連續發送/接收,減輕了CPU負擔;發送和接收均支持中斷方式,實時性高[7]。

SPI接口電路設計

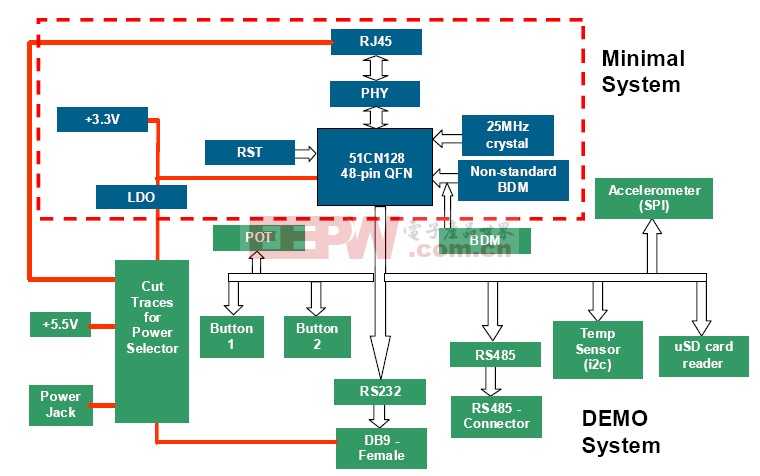

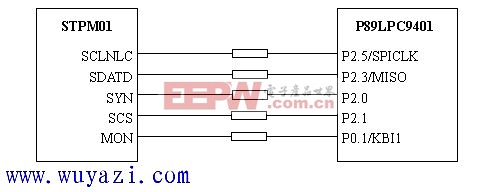

接口電路設計如圖2所示。其中SPISTE為從機使能信號, SPISIMO為主機發往從機的串行數據信號, SPISOMI為從機發往主機的串行數據信號, SPICLK為同步時鐘信號。以上信號構成SPI通信協議所規定的4線制結構。另外,利用主機和從機的各3個I/O引腳作為握手信號,解決了SPI總線中從機無權發起數據傳輸的缺陷,并引入校驗重發機制,進一步提高了數據通信的可靠性。

底層驅動設計

SPI模塊初始化

(1) 主/從模式選擇。考慮到系統在實際工作中,需由飛控DSP確定整個系統的運行時序,由飛控DSP決定是否讀取以及何時讀取導航DSP的解算結果,故將飛控DSP作為主機,導航DSP作為從機。

(2) 數據格式設定。程序每次寫入發送緩沖寄存器的數據長度以及每次從接收緩沖寄存器讀出的數據長度均為16 bit。

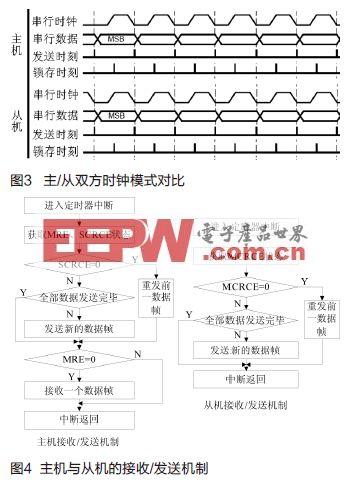

(3) 時鐘模式選擇。SPI協議使用串行時鐘同步主/從雙方的收/發操作,故一方的發送時刻與另一方的接收時刻必須嚴格匹配,否則將導致接收數據錯位甚至丟失。綜合比較4種時鐘模式后認為,將主方配置為D模式,從方配置為A模式符合要求。圖3給出了該種配置的時序對比。從圖3可知,主機在串行時鐘上升沿的半個周期之前發送數據,在串行時鐘的上升沿接收數據;從機在串行時鐘的下降沿發送數據,在串行時鐘的上升沿接收數據。因此,接收方鎖存數據的時刻總是比發送方發送數據的時刻延遲半個時鐘周期,能夠保證將數據準確鎖存。

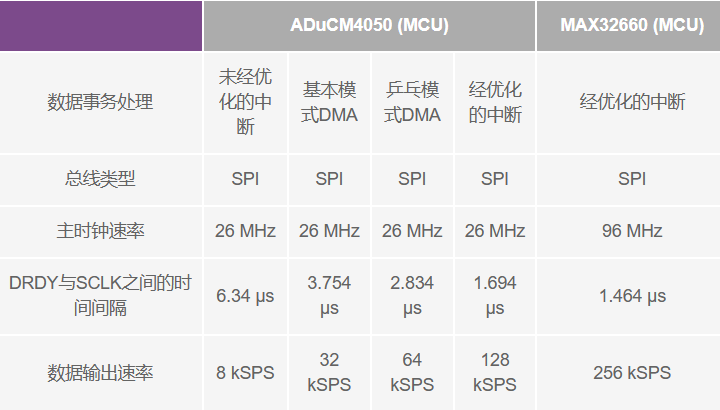

(4) 發送FIFO設置。發送FIFO通常與中斷模式配合使用。主機與從機的發送FIFO中斷觸發閾值均設為0,即當發送FIFO為空時觸發中斷。注意,在初始化完成后,發送FIFO為空,滿足發送中斷的觸發條件,而此時并不需要發送數據,因此必須屏蔽發送中斷。

(5) 接收FIFO設置。接收FIFO也是與中斷模式配合使用。主機與從機的接收FIFO中斷閾值均設為16,即當接收FIFO滿16個字時觸發中斷。

主機發送/從機接收的驅動設計

(1) 主機發送數據的驅動設計。主機首先將待發送的數據全部準備完畢,然后使能發送中斷,在中斷服務函數中將16字數據寫入發送FIFO,硬件電路將自動開始發送,待發送FIFO為空時寫入下個數據幀,如此往復,直至數據全部發送完畢,然后屏蔽發送中斷,完成本次發送操作。

(2) 從機接收數據的驅動設計。當接收FIFO內存滿一個數據幀后觸發接收中斷,在中斷服務函數中將此數據幀讀出。

通信相關文章:通信原理

評論