I2C總線通信技術在球形機器人雙DSP控制系統中的應用

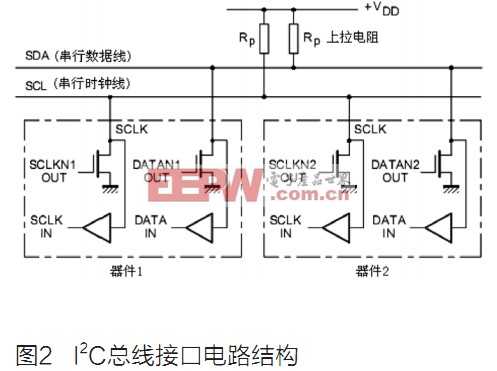

采用I2C總線標準的I2C器件,其內部不僅有I2C接口電路,而且實現了將內部各單元按功能劃分為若干相對應獨立的模塊,通過軟件尋址實現片選,減少了器件片選線的連接。CPU不僅能通過指令將某個功能單元掛靠和摘離總線,還可對單元的工作狀況進行檢測,從而實現對硬件系統簡單和靈活的擴展和控制。I2C接口電路結構如圖2所示。

本文引用地址:http://www.j9360.com/article/116960.htm

I2C總線上的時鐘信號

在I2C總線上傳送信息時的時鐘同步信號是由掛接在SCL時鐘線上的所有器件的連接“與”完成的。SCL線上由高電平到低電平的跳變將影響到這些器件,一旦某個器件的時鐘信號下跳為低電平,將使SCL線上一直保持低電平,使SCL線上的所有器件開始低電平期。此時,低電平周期短的器件的時鐘由低至高的跳變并不能影響SCL線的狀態,于是這些器件將進入高電平等待的狀態。

當所有器件的時鐘信號都上跳為高電平時,低電平期結束,SCL線被釋放返回高電平,即所有的器件都同時開始它們的高電平期。其后,第一個結束高電平期的器件又將SCL線拉成低電平。這樣就在SCL線上產生一個同步時鐘。可見,時鐘低電平時間由時鐘低電平期到最長的器件確定,而時鐘高電平期由時鐘高電平期最短的器件確定。

I2C總線上的數據傳輸

在數據傳送過程中,必須確認數據傳送的開始和結束。在I2C總線技術規范中,開始和結束信號(也稱啟動和停止信號)的定義如圖3所示。

當時鐘線SCL為高電平時,數據線SDA由高電平跳變為低電平定義為“開始”信號;當SCL線為高電平時,SDA線發生低電平到高電平的跳變為“結束”信號。開始和結束信號都是由主器件產生。在開始信號以后,總線即被認為處于忙狀態;在結束信號以后的一段時間內,總線被認為是空閑的。

I2C總線的數據傳送格式是:在I2C總線開始信號后,送出的第一個字節數據是用來選擇從器件地址的,其中前7位是地址碼,第8位是方向位(R/W)。方向位“0”表示發送,即主器件把信息寫到所選擇的從器件;方向位為“1”表示主器件將從從器件讀信息。開始信號后,系統中的各個器件將自己的地址和主器件送到總線上的地址進行比較,如果與主器件發送到總線上的地址一致,則該器件即為主器件尋址的器件,其接收信息還是發送信息則由第8位(R/W)確定。

I2C接口的硬件設計

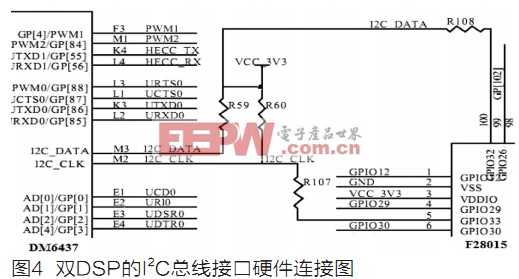

由于DM6437和F28015都支持I2C接口,這使得I2C接口的硬件設計變得非常簡單,只需將各自的信號線和時鐘線對應相連即可。雙DSP的I2C總線接口硬件連接圖如圖4所示。各引腳連接說明如下:

① DM6437的M3和M2引腳分別對應I2C_DATA和I2C_CLK,而F28015的GPIO32和GPIO33可以分別復用為I2C_DATA和I2C_CLK 。考慮到阻抗不匹配等因素會影響總線數據傳輸效果,因此還應該在I2C_DATA和I2C_CLK 的直連線路上各串聯一個小電阻(R107和R108)。

② 由3.1.1節的I2C總線結構介紹可知,I2C_DATA和I2C_CLK是雙向電路,必須都通過一個電流源或上拉電阻連接到正的電源電壓。由于DSP的輸出CMOS電平為3.3V,所以在硬件設計時將I2C_DATA和I2C_CLK總線通過上拉電R59和R60連接到了3.3V的Vcc電源上。

評論