基于CPLD內(nèi)部的反向器實現(xiàn)振蕩器應用

振蕩器實現(xiàn)

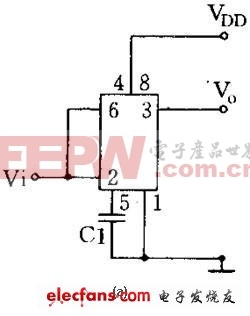

本文引用地址:http://www.j9360.com/article/113013.htm利用CPLD內(nèi)部的施密特觸發(fā)器使輸入波形得到校正,再加上反向器反向和外部RC實現(xiàn)振蕩器,只需要在使用CPLD的任意兩個I/O PIN引腳(當然從CPLD內(nèi)部原理來看最好是使用相鄰的兩個PIN引腳,會減小CPLD內(nèi)部資源的占用)。其中一個PIN 引腳串入電阻,外接一個對地電容,當內(nèi)部的A點為高電平時,PIN1會通過R1對C1充電,由于電容的電壓不可越變,電壓是對電流的積分,所以電壓會逐漸上升,當電平上升至0.5 × VCCIO,CPLD施密特觸發(fā)器才認為是高電平,再經(jīng)過內(nèi)部的反向器會反向,所以A 點會變成低電平,這時C1 會通過R1逐漸放電,當放電電平低于0.5 x VCCIO時,反向器反向A點又變回高電平,這樣反復的振蕩就構(gòu)成了一個穩(wěn)定的振蕩器時鐘源(見表1)。

CPLD實現(xiàn)代碼

本設計使用VHDL語言,選用XILINX 公司的COOLRUNNER-II系列的CPLD器件, 基于0.18nm CMOS CPLD, 3.8ns PIN-to-PIN延時,快速JTAG下載,2個bank,具體實現(xiàn)見代碼列表。

振蕩器應用

上述代碼通過XILINX的編譯綜合器后,會產(chǎn)生一個可下載檔案,此檔案可以通過JTAG直接下載到芯片中使用,由于代碼示例的為一個實時振蕩器,也就是只有芯片上電,振蕩器部分會一直工作,對于用于電源管理的嵌入式產(chǎn)品設計,由于一直振蕩帶來額外的電功耗損耗,功耗的損耗和振蕩的頻率是相關的,當頻率越高時,功耗越大。所以,設計還可以再被優(yōu)化使用。比如,當符合什么條件時振蕩器才開始振蕩,或者達到什么條件時振蕩器停止振蕩,這樣靈活的優(yōu)化設計會給產(chǎn)品帶來更多的附加價值,延長電池的使用壽命。

振蕩器的振蕩頻率是通過外部引腳的電阻和電容來調(diào)整的,當電阻越小,電容越小時,振蕩的頻率就很高。當電阻很大時,電容也變大,振蕩的頻率就會變低。振蕩器的精度取決于外面電阻和電容的精度,電阻的精度以現(xiàn)在工藝可以做到1%的正負誤差,電容可以選擇5%的正負誤差,高精度的電阻和電容會帶來比較精準的振蕩頻率。

評論