高速高精度流水線模數轉換器的設計

第一版芯片測試結果及分析

本文引用地址:http://www.j9360.com/article/112970.htm

第一版芯片測試結果及分析

在輸入信號頻率為2.41MHz,幅度接近2Vp-p時,采樣率從15.5MHz增加到100MHz,ADC的SNDR和SFDR分別大于57.9dB和68.9dB。另外測得該芯片的DNL為-1.0/+0.2LSB,INL為-5.0/+5.0LSB。

如圖3中(a)和(c)是在30MHz采樣率、2.41MHz輸入信號下測得的INL和FFT曲線。INL為-5.0/+5.0LSB,SFDR為68.9dB,SNDR為58.4dB。無論是動態性能還是靜態性能,對于一個12bit的ADC來說這個結果顯然不能令人滿意。通過觀察靜態特性曲線,可以發現曲線很有規律,每隔256個碼就會出現一個拐點,這是因為每隔256點就出現失碼現象,共有14處失碼,與ADC第一級3.5bit傳輸曲線的折線位置重合,故推斷可能是第一級電路出了問題。

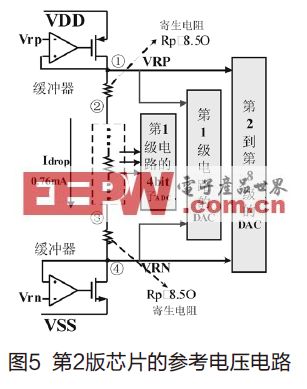

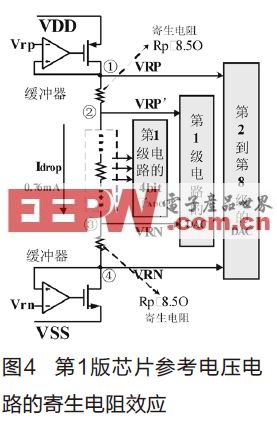

通過對版圖的仔細分析,發現版圖中存在一個嚴重的問題。如圖4所示的參考電壓產生電路,Vrp和Vrn的緩沖電路(bu er)采用的是開漏結構的兩級運放,在Vrp和Vrn的緩沖器之間串聯了一組電阻用來產生第1級電路中3.5位flash ADC所需的14個比較電平。如果不考慮寄生電阻,節點1和2是重合的,第一級的參考電壓VRP’和其它各級的參考電壓VRP相等,VRN和VRN’也是如此。但是由于導線都會有電阻,所以實際情況是節點1和2之間,3和4之間有寄生電阻Rp,而Vrp和Vrn的驅動電路均是開漏結構,在節點1到節點4之間存在靜態電流Idrop,這個電流流過Rp就造成了節點1和2之間的壓差:

![]()

節點3和4之間的情況與之一樣。經過估算Rp的值大約為8.5Ω,而Idrop約為0.76mA,所以 V為6.5mV。在畫版圖時,沒有考慮寄生電阻的影響,給第1級級電路DAC用的參考電壓直接就近從節點2和3引出,因此造成了第1級的參考電壓VRP’和VRN’與后面各級的參考電壓VRP和VRN存在 V的差值,因此,第一級電路的參考電壓為:

![]()

后面各級電路的參考電壓為:

![]()

由于第1級電路的參考電壓比其它各級都小,ADC出現失碼現象。為了進一步分析第1級參考電壓偏小會對ADC靜態特性和動態特性產生多大的影響,我們用Matlab來行為級建模仿真,并與30MHz采樣率下的INL、SFDR和SNDR做對比。

建模主要基于如下兩個前提:

(1)第1級的參考電壓為:Vref’=0.987V

其它各級的參考電壓為:Vref=1V

(2)不考慮噪聲、失配、運放有限增益和有限帶寬等非理想因素。

如圖3中的(b)和(d)所示為ADC行為級仿真結果。行為級仿真的INL為-4.2/+4.4 LSB,SFDR為65dB,SNDR為59.2dB。由圖可知仿真結果很好得再現了實際測試結果,第1級參考電壓偏小不僅加重了ADC的奇次諧波失真,也造成了很大的偶次失真。綜合來說,第1級參考電壓的偏小會對ADC靜態特性和動態特性造成很大的影響,通過模擬仿真較好地解釋了實測時ADC靜態特性和動態特性很差的原因。

模數轉換器相關文章:模數轉換器工作原理

電荷放大器相關文章:電荷放大器原理 電容傳感器相關文章:電容傳感器原理

評論