用于CMOS圖像傳感器的流水線ADC設計及其成像驗證

CMOS圖像傳感器(CMOS image sensor,CIS)在近二十年來取得了飛速的發展,得益于有源像素傳感器(Active PixelSensor)的出現、相關雙采樣技術(Correlated Double Sampling)的發明以及工藝的進步等,用于低噪聲應用領域的CMOS圖像傳感器也取得了長足的發展。由于CMOS傳感器具有先天的低成本、易于集成等優點,CMOS傳感器在低噪聲應用領域也已引起了越來越多的關注。目前,在低噪聲CMOS圖像傳感器的研究領域,除研究其噪聲外,數字化也是它的一個重要的研究方向。

文中介紹了一種適用于低噪聲CMOS圖像傳感器芯片級模數轉換的流水線型ADC,根據低噪聲CMOS圖像傳感器的系統要求,文中設計的ADC的分辨率為12 bit,速度為10 Msps,采用了每級1.5 bit、共11級的流水線型結構。在該ADC完成設計仿真后,基于0.5μm標準CMOS工藝進行了流片。最后在PCB板級電路上用該ADC對一個自主設計的模擬輸出的CMOS圖像傳感器進行了模數轉換,并基于自主設計的成像測試系統完成了CMOS圖像傳感器的成像。

1 ADC設計指標及框架

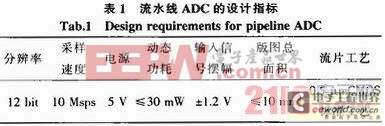

根據自主設計的低噪聲CMOS圖像傳感器的系統要求,可以確定流水線ADC的設計指標。表1給出了該設計的具體設計指標。

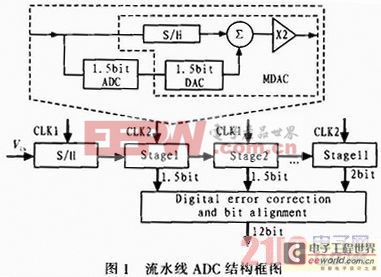

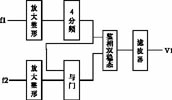

由于該ADC設計目標為應用在自主設計的低噪聲CMOS圖像傳感器的芯片級,因此其速度和精度都應盡可能的高,以達到芯片系統低噪聲和速度的要求。而由于其工作在芯片級,其功耗和面積的要求則可以相對寬松一些。因此本設計采用了11級,1.5 bit每級的結構,雖然這種結構在功耗上會有所增加,但是可以降低比較器的比較精度帶來的影響,同時也降低了對第一級采樣保持電路運放的要求。本文設計的ADC的結構框圖如圖1所示,在該ADC11級結構中的前10級電路中,每級電路包括子模數轉換器(ADC)、子數模轉換器(DAC)、求和電路、余量放大器以及采樣保持電路,其中由于子DAC、采樣保持電路、求和電路以及余量放大電路一般都由一個開關電容電路實現,因此該電路模塊常被統稱為乘法型數模轉換器(Multiplying digital to analog converter,MDAC),第11級電路為一個2 bit的flash ADC。在兩組互不相交時鐘CLK1和CLK2的控制下,每級電路都產生了數字輸出,這些輸出在經過數字位對齊和數字校準后得到最終的數字輸出。

2 ADC各模塊設計

2.1 MDAC設計

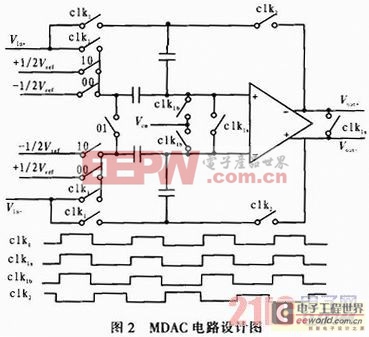

MDAC電路是流水線ADC設計中非常重要的部分,它在ADC中實現的功能包括采樣保持、數模轉換、減法和余量放大等,一般采用開關電容技術實現,由模擬開關、電容和跨導運算放大器(OTA)構成,其電路圖如圖2所示。其工作原理是:用MDAC的采樣保持對前級余量電壓進行采樣;將其采樣電壓與本級子DAC的輸出電壓進行減法運算;將減法運算得到的余量電壓通過余量放大器進行放大。

在流水線ADC結構中,第一級的MDAC的要求最高,隨著級數的增加,要求不斷降低。對于一個12位、10 Msps采樣率流水線ADC,以第一級MDAC為例,該電路需滿足的總體指標為:精度12 bit,采樣率10 Msps。而在MDAC設計中,最關鍵的是余量放大器設計,本文以第一級余量放大器的設計為例來說明整個設計,其中采用的余量放大器的結構如圖3所示。余量放大器工作在閉環狀態,要求其有限直流增益造成的誤差小于1/2LSB,即有:

![]()

式中A0為開環增益,N為ADC分辨率,β為反饋系數。

評論