基于JTAG邊界掃描方式的重構控制器的設計

仲裁與時序控制模塊

本文引用地址:http://www.j9360.com/article/105941.htm仲裁與時序控制模塊主要完成對重構控制器內部各模塊的仲裁與時序控制。協調各模塊之間的數據流向。其具體的功能包括提供內部各模塊所需的時鐘信號,并進行相應的時序控制;以及對內部數據流的切換控制。

TCK,TMS,TDI,TDO產生模塊

TCK: JTAG配置時鐘輸入,所有基于JTAG的操作都必須同步于JTAG時鐘信號TCK。關鍵時序關系是:TMS和TDI采樣于TCK的上升邊沿,一個新的 TDO值將于TCK下降邊沿后出現,因此一般情況下JTAG的時鐘不會太高。

TMS:模式選擇,控制JTAG狀態轉移,同步時鐘TCK上升沿時刻TMS的狀態決定狀態轉移過程。

TDI :配置數據輸入,配置數據在TCK的上升沿采樣進入數據移位寄存器(SDR);

TDO:配置數據輸出,在TCK的下降沿從移位寄存器移出,輸出數據與輸入到TDI的數據應不出現倒置。

目標板

目標板上被重構的FPGA由支持重構的Xilinx公司的VIRTEX-4系列FPGA來實現,以菊花鏈方式串聯,支持JTAG邊界掃描模式配置。

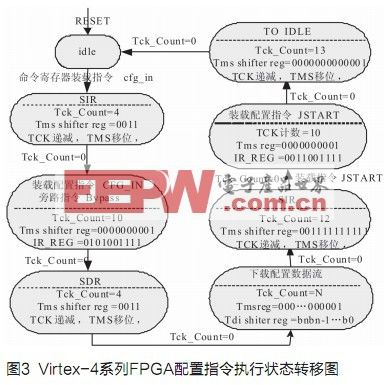

TAP控制器是16個狀態的有限狀態機,主要為JTAG接口提供控制邏輯。主要有四大狀態:復位(RESET),空閑(idle),數據寄存器移位(SDR)和指令寄存器移位(SIR)狀態, 在TCK,TMS的控制下,根據輸入的配置指令實現狀態的轉移。Xlinx公司Virtex4系列 FPGA器件的邊界掃描指令集中有三條專用于配置的邊界掃描指令:CFG_IN、BYPASS和JSTART(10個bit位)。其中CFG_IN的代碼:0101001111;BYPASS的代碼:1111111111;JSTART的代碼:0011001111。執行CFG_IN指令可以訪問器件內部的配置總線,通過串行移入配置文件中的命令和數據執行對內部配置寄存器的讀寫,從而完成對FPGA的配置。BYPASS指令在對多個目標器件配置時可以旁路不需要重配置的器件。JSTART指令使用TCK時鐘觸發啟動時序,使FPGA完成從配置狀態到操作狀態的轉換,激活FPGA。圖3為可重構控制器模擬TAP狀態機配置指令執行的狀態轉移圖。

評論