基于NIOS II的BCMO4藍牙通信模塊的設計

本設計采用了Altera公司開發的第二代低成本的FPGA芯片,在其之上開發了基于BCM04的NIOSⅡ藍牙通信模塊。該通信模塊能夠代替電纜,有效的應用于工作環境復雜多變的工業現場,可實現與現場設備、接入點、手操器等設備的無線通信

本文引用地址:http://www.j9360.com/article/104105.htm引言

在工業現場中,大多的通信設備是通過加裝通信模塊來實現的,而大多的通信模塊的處理器采用ARM核。隨著微電子學和計算機科學的迅速發展,電子系統已經從電路板級系統集成發展成為包括ASIC、FPGA和嵌入式系統的多種模式。SOPC由于集成了硬核或軟核CPU、DSP、存儲器、外圍I/O及可編程邏輯模塊,在設計和應有的靈活性及其成本方面有較大的優勢。

NIOSⅡ系列處理器是Altera公司的第二代FPGA嵌入式處理器。同前一代軟核的CPU相比,NIOSⅡ的性能得到很大提高,體積更小,其最大處理能力是第一代軟核的三倍。邏輯功能方面具有32位的精簡指令集CPU。實現方式是在FPGA上通過編程的方式實現,這是與傳統的CPU的一個根本的差別。本文是在NIOSⅡ軟核的基礎上設計了藍牙通信模塊,并在工業以太網中,較好地實現了通信模塊與工業現場設備的無線通信。

NIOSⅡ嵌入式處理器概述

NIOSⅡ處理器是Altera公司的第二代用戶可配置的通用32位RSIC軟核微處理器,是Altera公司特有的基于通用FPGA架構的軟CPU內核。它可以提供:完全的32位指令集、數據總線和地址空間;32位通用的目的寄存器;32個外部中斷源;計算64位和128位乘積專用指令;單指令桶形移位器;對多種片上外設進行訪問,提供片外存儲器和外設接口;在IDE控制下,硬件輔助調試模塊可對處理器進行啟動、停止、單步和追蹤操作;基于CNU C/C++工具鏈和Eclipse IDE;所有的NIOSⅡ處理器系統的指令集兼容;具有超過150 DMIPS的性能。

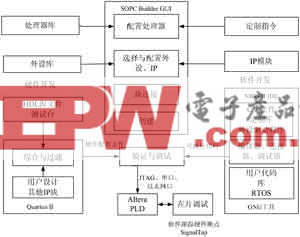

它將設計輸入、綜合、布局、驗證、編程與配置以及第三方EDA工具接口集成在一個無縫的綜合性設計環境中。NIOSⅡ的硬件開發環境是在SOPC builder中進行的。SOPC builder是一個自動化的SOPC硬件系統的開發工具,集成在Quartus Ⅱ軟件內,Quartus Ⅱ和SOPC builder一起為建立SOPC設計提供標準化的圖形環境。Quartus Ⅱ和SOPC builder軟件,可以在很短的時間內定義一個完整的硬件系統。SOPC builder 通過SOPC開發階段的系統定義、集成和驗證的自動化,縮短了產品的市場化時間。

NIOSⅡ軟件開發環境被稱為NIOSⅡ集成開發環境(Integrated Development Environment,IDE)。它內嵌在Quartus Ⅱ設計工具中,可通過JTAG將應用程序下載到SOPC硬件系統中進行調試,可在指令集仿真器中對應用程序進行仿真調試,也可在ModelSim軟件中進行仿真調試。基于NIOSⅡ的SOPC的軟硬開發環境及設計流程如圖1所示。

圖1 基于NIOSⅡ的SOPC軟硬件開發環境及流程

首先利用SOPC Builder的界面定制系統,產生輸出文件;然后進入傳統的FPGA硬件開發流程;在Quartus Ⅱ中進行邏輯綜合、布局布線。在軟件流程中,用戶利用NIOSⅡ IDE環境,建立工程、編譯設計、調試等。

藍牙通信模塊的硬件設計

藍牙技術是一個開放性的、短距離無線通信技術標準,工作在全球通用的2.4GHz ISM頻段,采用跳頻擴頻技術,可以用于近距離通過無線連接的方式實現固定設備以及移動設備之間的網絡互連,在各種數字設備之間實現靈活、安全、低成本、小功耗的數據和語音通信,實現全方位的數據傳輸。

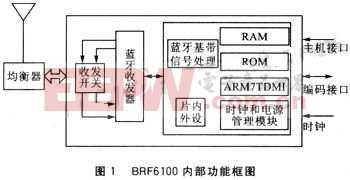

工業現場中存在多種使用不同方法進行互連的設備。對有些環境比較惡劣,布線不方便等因素可以采用藍牙無線通信技術來實現數據的通信。本設計中,采用了基于NIOSⅡ軟核的FPGA芯片EP1C12Q240C8作為CPU處理器,并在處理器的外圍拓展了64Mb的SDRAM和16Mb的Flash,配置了50MHz的時鐘、復位電路、下載口,接入藍牙模塊,以便在藍牙通信模塊中實現通信協議并通過藍牙模塊發送測試數據或接收控制命令等。圖2為基于NIOSⅡ軟核的藍牙通信模塊的硬件設計框圖。

圖2 基于NIOSⅡ軟核的藍牙通信模塊的硬件設計框圖

評論