實驗8:4位奇偶校驗器

Warning: file_get_contents(https://www.eetree.cn/wiki/_media/4%E4%BD%8D%E5%A5%87%E5%81%B6%E6%A0%A1%E9%AA%8C%E5%99%A8%E7%9C%9F%E5%80%BC%E8%A1%A8.png?w=300&tok=02a86b): failed to open stream: HTTP request failed! HTTP/1.1 403 Forbidden in /var/www/html/www.edw.com.cn/www/rootapp/controllersspace/ArticlesmanageController.php on line 270 Warning: file_get_contents(https://www.eetree.cn/wiki/_media/%E9%80%BB%E8%BE%91%E7%94%B5%E8%B7%AF4%E4%BD%8D%E5%A5%87%E5%81%B6.png?w=300&tok=64a86f): failed to open stream: HTTP request failed! HTTP/1.1 403 Forbidden in /var/www/html/www.edw.com.cn/www/rootapp/controllersspace/ArticlesmanageController.php on line 270

實驗目的設計一個4位奇偶校驗器電路。要求當輸入的4位二進制碼中有奇數個“1”時,輸出為“1”,否則輸出為“0”。

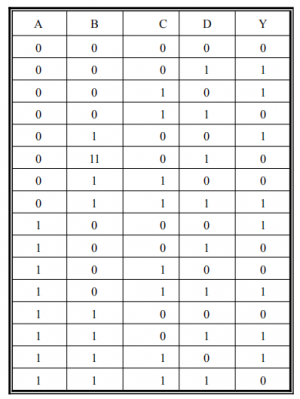

奇偶校驗,即判斷輸入變量中1的個數。當輸入變量中1的個數是奇數時,輸出為1。當輸入變量中1的個數是偶數時,輸出為0。真值表及邏輯表達式如下所示:

Y=A’B’C’D+A’B’CD’+A’BC’D’+A’BCD+AB’C’D’+AB’CD+ABC’D+ABCD’

經過化簡得到:Y=A⊕B⊕C⊕D

4選1多路選擇器程序清單mult4.v

module parity4 ( input wire a,b,c,d, //定義4個輸入 output wire led //定義奇偶校驗輸出結果對應的led ); assign led = a^b^c^d; //根據邏輯表達式賦值 endmodule

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。