PCB設(shè)計(jì):任意層過孔技術(shù)特點(diǎn)及設(shè)計(jì)挑戰(zhàn)

近些年來,為了滿足一些高端消費(fèi)類電子產(chǎn)品小型化的需要,芯片的集成度越來越高,BGA管腳間距越來越近(小于等于0.4pitch),PCB的布局也越來緊湊,走線密度也越來越大,為了提高設(shè)計(jì)的布通率且不影響信號(hào)完整性等性能,ANYLAYER(任意階)技術(shù)應(yīng)用而生,這個(gè)就是任意過孔技術(shù)(ALIVH-Any Layer IVH Structure Multilayer Printed Wiring Board)。

任意層過孔技術(shù)特點(diǎn)

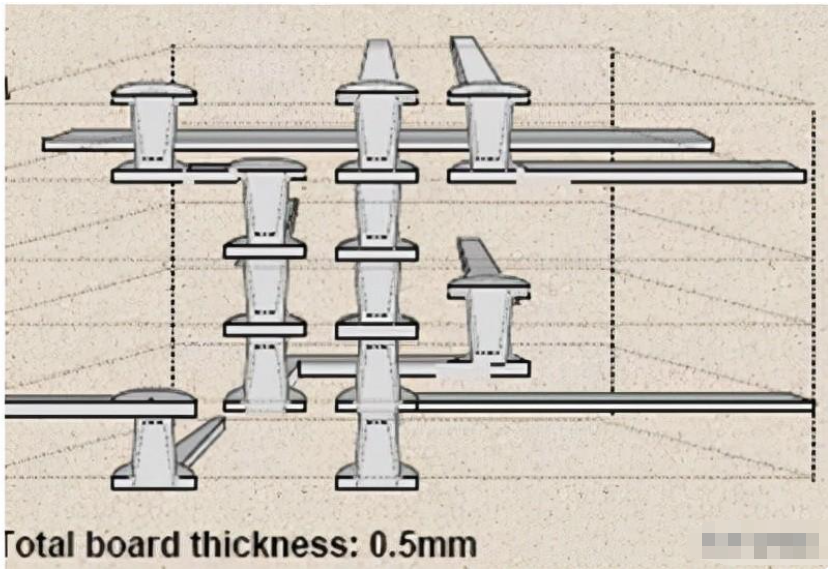

任意層過孔技術(shù)與HDI技術(shù)的特征比較,ALIVH的 優(yōu)勢(shì)就是設(shè)計(jì)自由度大大增加,可以在層間隨意打孔,而HDI工藝不能做到這點(diǎn)。一般國內(nèi)廠商做到 復(fù)雜的結(jié)構(gòu)也就是HDI的設(shè)計(jì)極限為三階HDI板,由于HDI不是完全采用激光鉆孔,在內(nèi)層的埋孔采用的是機(jī)械孔,所以孔盤的要求比激光孔大很多,而機(jī)械孔要占用所經(jīng)過的層面上空間。所以一般來說HDI這種結(jié)構(gòu)比起ALIVH技術(shù)的任意打孔,內(nèi)層核板的孔徑也可用0.2mm的微孔還是有很大差距的。所以ALIVH板的走線空間比HDI大概有很大的提高。同時(shí),ALIVH的成本和加工難度也比HDI工藝要高。如圖三所示,是一個(gè)ALIVH的示意圖。

圖三 ALIVH的示意圖

任意層過孔的設(shè)計(jì)挑戰(zhàn)

任意層過孔技術(shù)完全顛覆了傳統(tǒng)過孔設(shè)計(jì)方法。如果還是需要設(shè)置不同層的過孔,會(huì)增加管理難度。需要設(shè)計(jì)工具具備智能化打孔的能力,同時(shí)能隨意的進(jìn)行組合和拆分。

Cadence在傳統(tǒng)的基于換線層的布線方式上,增加了基于Working Layer的換線方式,如圖四所示:可以在Working Layer面板中勾選可以進(jìn)行環(huán)線的層,然后在雙擊打孔的時(shí)候,就可以選擇任意層之間進(jìn)行換線。

20121017091918261.jpg

圖四 基于Working Layer的布線方式

ALIVH設(shè)計(jì)制板實(shí)例:

10層ELIC設(shè)計(jì)

OMAP4 Platform

埋阻、埋容和埋入式元器件

對(duì)高速訪問互聯(lián)網(wǎng)和社交網(wǎng)絡(luò)要求手持設(shè)備高集成和小型化。目前靠 的4-N-4的HDI技術(shù)。但為了下一代新技術(shù),實(shí)現(xiàn)更高的互連密度,在這個(gè)領(lǐng)域,埋入無源甚至于有源的零件進(jìn)入PCB和基板中可滿足以上要求。當(dāng)你設(shè)計(jì)手機(jī),數(shù)碼相機(jī)等消費(fèi)類電子產(chǎn)品,考慮如何將無源和有源的零件埋入PCB和基板是當(dāng)前設(shè)計(jì)的 選擇。這種方法可能因?yàn)槟悴捎貌煌墓?yīng)商略有不同。埋入零件的另外一個(gè)好處,該技術(shù)提供對(duì)知識(shí)產(chǎn)權(quán)保護(hù),防止所謂的逆向設(shè)計(jì)。Allegro PCB Editor可以提供 的工業(yè)級(jí)解決方案。Allegro PCB Editor還可以同HDI板,柔板和埋入式零件更加緊密的合作。你可以得到正確的參數(shù)和約束對(duì)完成埋入式零件的設(shè)計(jì)。埋入器件的設(shè)計(jì)不僅可以簡化后面SMT的工藝,同時(shí)對(duì)產(chǎn)品表明的整潔度都有很大的提高。

埋阻、埋容設(shè)計(jì)

埋阻又稱埋電阻或者薄膜電阻,是將特殊的電阻材料壓合在絕緣基材上,然后通過印刷,蝕刻等工藝,得到所需電阻值,然后與其他PCB板層一起壓合,形成平面電阻層。常見的有PTFE埋電阻多層印制板制造技術(shù),可以達(dá)到所需的電阻 。

埋電容則是利用具有較高電容密度的材料,同時(shí)減少層間的距離,來形成一個(gè)足夠大的平板間電容,來起到電源供電系統(tǒng)的去耦和濾波作用,從而減少板子上所需的分立電容,并且能達(dá)到更好的高頻濾波特性。埋容由于其寄生電感非常小,其諧振頻率點(diǎn)會(huì)比普通電容或者低ESL電容效果都好。

由于工藝和技術(shù)的成熟,以及高速設(shè)計(jì)對(duì)于電源供電系統(tǒng)的需要,埋容的技術(shù)應(yīng)用越來越多,使用埋容技術(shù),我們首先得計(jì)算平板電容的大小 圖六 平板電容計(jì)算公式

其中:

C是埋容(平板電容)的電容量

A是平板的面積,大部分設(shè)計(jì)在結(jié)構(gòu)確定的情況下,平板間面積很難增大

D_k是平板間介質(zhì)的介電常數(shù),平板間電容量和介電常數(shù)成正比

K是真空介電常數(shù)(Vacuum permittivity),又稱真空電容率,是一個(gè)物理常數(shù),值為8.854 187 818× 10-12法拉/米(F/m);

H是平面之間的厚度,平板間電容量和厚度成反比,所以我們想要得到較大的電容量,需要減小層間厚度,3M的C-ply埋容材料可以做到0.56mil的層間介質(zhì)厚度,加上16的介電常數(shù),大大增加了平板間電容量。

經(jīng)過計(jì)算,3M的C-ply埋容材料,在每平方英寸的面積上,能實(shí)現(xiàn)6.42nF的平板間電容量。

同時(shí),還需要使用PI仿真工具進(jìn)行PDN目標(biāo)阻抗的仿真,從而確定單板的電容設(shè)計(jì)方案,避免埋容和分立電容的冗余設(shè)計(jì)。圖七是一個(gè)埋容設(shè)計(jì)的PI仿真結(jié)果,只考慮板間電容的效果,沒有加入分立電容的效應(yīng)。能看到只是增加埋容,整個(gè)電源阻抗曲線性能得到很大提升,尤其是500MHZ以上,是板級(jí)分立濾波電容很難起作用的頻段,平板電容能有效降低電源阻抗。

*博客內(nèi)容為網(wǎng)友個(gè)人發(fā)布,僅代表博主個(gè)人觀點(diǎn),如有侵權(quán)請(qǐng)聯(lián)系工作人員刪除。