臺積電談逆光刻技術的過去、現在和未來

來源:本文由半導體行業觀察編譯自Semiwiki。

逆光刻技術 (IInverse lithography technology:ILT) 代表了過去二十年來 EDA 最重要的進步。” 臺積電的彭丹平(Danping Peng )在最近的 SPIE 高級光刻 + 圖案化會議上發表了這一論斷,他的演講題為《用于 HVM 的 ILT:歷史、現在和未來》。

本文總結了他富有洞察力的演講的亮點。事實上,ILT 已經提高了以更高的保真度打印晶圓級特征的能力。

ILT 歷史

首先,簡要回顧設計流片后與掩模制造相關的步驟:

? 掩模車間將光學鄰近校正 (OPC) 或 ILT 算法應用于掩模數據。

? 掩膜數據準備 (Mask data prep:MDP) 將以適合掩碼寫入器的格式組合 OPC/ILT 生成的數據。

? 掩模寫入已經從(基于光學的)圖案生成光刻膠涂層掩模坯的曝光發展到基于電子束的曝光。可變形狀光束 (VSB) 和多光束詢問書寫系統均可用。(稍后會詳細介紹。)

? 掩膜檢測步驟包括:

? 臨界尺寸 (CD) 計量 (CD-SEM)

? 使用航空影像測量系統(例如,Zeiss AIMS)進行掩模審查

? 掩模缺陷修復

然后掩膜進入晶圓廠,晶圓級印刷品將經過類似的步驟:CD-SEM 尺寸評估、晶圓檢測和缺陷分析。

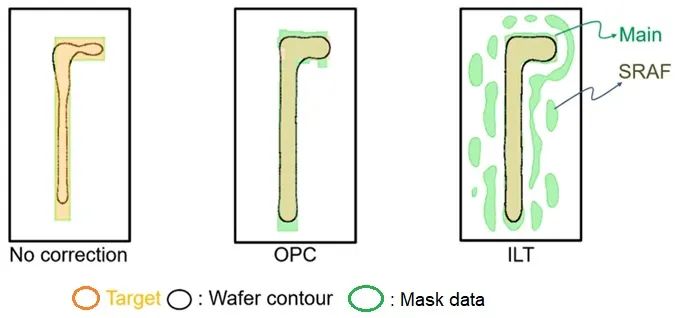

下圖中突出顯示了對掩模校正算法的需求。

隨著晶圓上的打印尺寸隨著連續的工藝節點而縮放,圖像的保真度——即目標圖像和打印的晶圓輪廓之間的差異——變得很差。需要更正版圖設計數據。

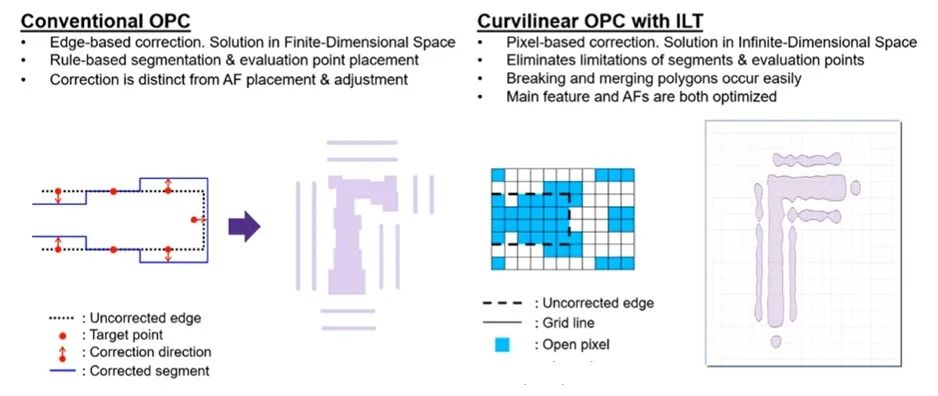

生成掩模更新的原始方法被稱為光學鄰近校正 (OPC)。(直線)設計數據中的各個部分以適當的間隔被一分為二,并且通常使用基于規則的算法來移動子部分。在形狀角處添加了矩形襯線——在外角處擴展段,在內角處縮小。(OPC 結果被賦予了不同的名稱——例如,“hammerheads”、“dogbones”。)

隨后,OPC 算法將亞分辨率輔助功能 (SRAF) 添加到掩膜碼數據中。這些是與原始設計不同的形狀,其尺寸是有意選擇的,以便不以晶圓光刻膠分辨率打印,但由于設計形狀邊緣的光學衍射提供適當的(建設性和破壞性)干涉。

如上圖和下圖所示,ILT 算法做出了根本不同的假設,利用曲線掩模數據進行校正和 SRAF。下圖說明了 OPC 的基于邊緣的性質與基于像素的 ILT 算法之間的主要區別。

ILT 的工作原理

Danping用下面兩張圖來說明ILT是如何工作的。下面的第一個圖是一個高級流程圖,提供了掩模數據生成和蝕刻后晶圓級計量之間的綜合(理想)迭代循環。(稍后將詳細介紹這個完整的循環。)

下圖提供了有關 ILT 流程的更多詳細信息。兩個相鄰的形狀用于說明。

計算強度的三維表示。計算誤差函數,其中包含構成元素的加權和。每個權重乘以與計算的打印圖像和跨像素場的硅片目標之間的差異相關的因子。

誤差函數可能包括來自各種印刷圖像特征的貢獻:

?標稱尺寸(打印到目標的差異)

?建模的三維光刻膠輪廓

?要抑制的目標區域外的像素光強度

?對照明劑量和焦點變化的敏感性

追求迭代優化以減少該誤差函數的大小。請注意,上圖提到了基于梯度的優化,以減少從模型預測和目標之間的差異計算得出的誤差函數——ILT 與機器學習方法的相似性很大,正如 Danping 在他的演講的 Futures 部分中強調的那樣。

當前 ILT 的采用和挑戰

在過去的二十年里,ILT 的采用一直存在障礙。丹平回顧了這些挑戰,以及如何應對這些挑戰。

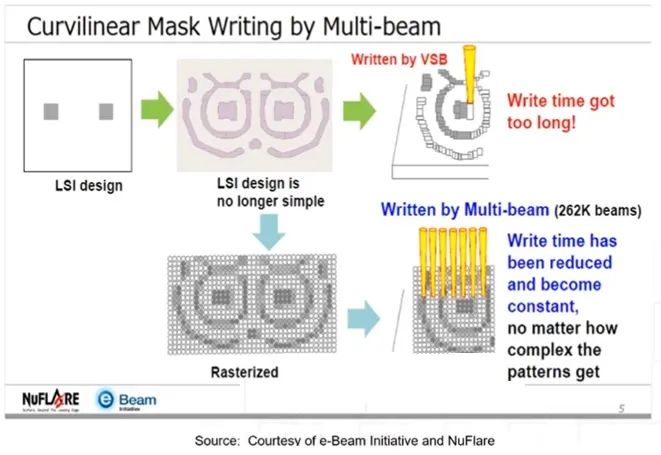

1. 掩膜寫入時間

與傳統 OPC 方法相比,曲線(基于像素)ILT 掩模數據提供了改進的焦深。然而,相應的數據復雜性導致使用可變尺寸光束 (VSB) 技術寫入掩模的電子束****次數大幅增加。

丹平解釋說:“當 ILT 最初被追求時,并沒有多光束掩模寫入器。因此,使用 VSB 系統曝光 ILT 掩膜需要數天時間。現在,使用多光束系統,掩模寫入時間基本恒定,大約 8 小時。”

請注意,ILT 數據生成應用了“中等約束”以幫助加快速度——例如,SRAF 區域/空間/CD 的最小設計規則,形狀數據曲率的最大限制。

2. ILT 掩碼數據生成時間

“ILT 的首次采用是由內存代工廠所采用的。”丹平表示。 “他們的布局具有高度重復性,經過精心制作,減少了重復模式的數量。”

邏輯設計的 ILT 采用速度較慢。丹平詳細闡述了其中的一些挑戰:

?計算運行時間長(“比 OPC 慢 20 倍”)

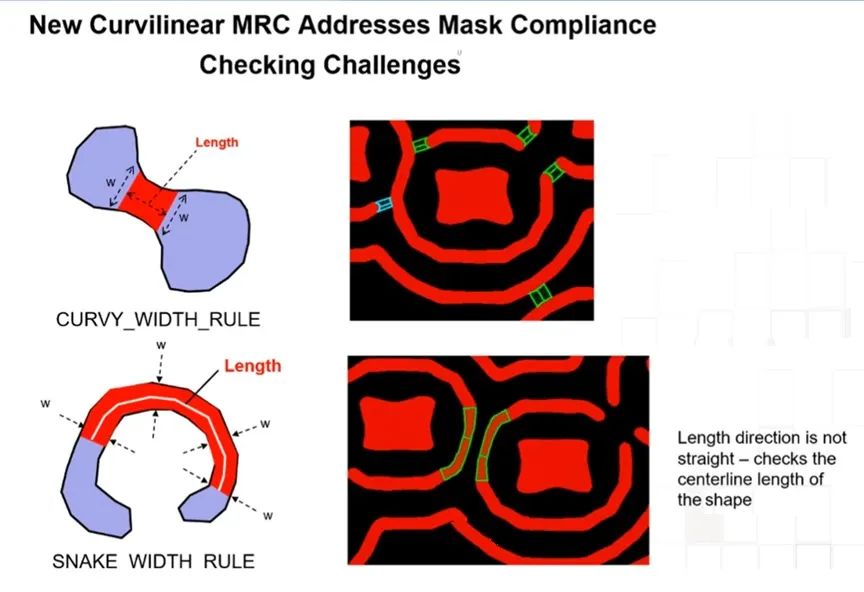

?曲線邊緣的掩模數據規則檢查技術滯后

?曝光系統的改進提高了圖像分辨率(例如,193 到 193i)和劑量均勻性,降低了 ILT 優勢

用于模型生成和誤差函數+梯度計算的 ILT 算法以矩陣運算為主。為了解決運行時挑戰,ILT 代碼已移植到基于 GPU 的計算資源中。根據 Danping 的說法,這提供了“比嚴格基于 CPU 的計算快 10 倍” 。

為了解決掩模數據驗證挑戰,SEMI Curvilinear Task Force 正在研究一種數據表示,該表示將作為模型交換的標準格式。(這也是由與硅光子結構相關的曲線設計布局數據驅動的。)下圖說明了新的“規則定義”,它將成為掩模數據檢查的一部分。

丹平就 ILT 相對于曝光系統改進的市場機會提供了以下觀察,“ILT 可用于從現有工具中榨取更多性能。” 從這個意義上說,ILT 可以擴展現有掃描儀的使用。

丹平分享了一個預測,“EUV 和 193i 掩模將在 2023 年普遍采用曲線形狀。” (來源:eBeam Initiative)

ILT 未來

丹平對 ILT 技術提出了三個預測。

1. 采用深度學習技術

如上所述,ILT 算法與深度神經網絡方法的計算和優化技術有很多共同之處。下圖說明了如何采用深度學習。

“經過訓練的深度學習模型可用于生成掩膜數據,然后進行少量 ILT 迭代。ILT 掩膜數據可以在之前運行時間的 15% 中獲得。” ,丹平提到。

2. 增加曲線設計數據的使用

除了硅光子結構,在先進工藝節點的電路布局中直接使用曲線數據的機會可能很快就會被采用。(考慮在 Mn+1 層上使用金屬“跳線”來改變 Mn 層上長信號的布線軌道的情況。)行業對曲線數據表示的支持將使這種可能性成為可能,盡管它也會對整個 EDA 工具流程。

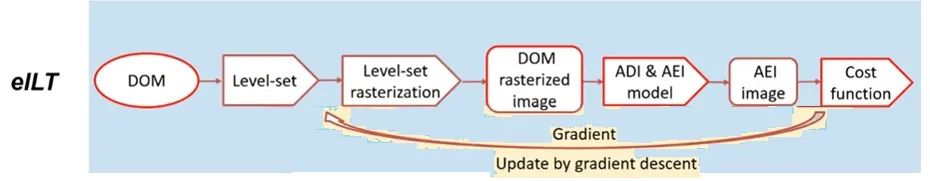

3. 指導 ILT 的完整“逆向蝕刻技術”(IET) 流程

較早的圖顯示了掩模數據生成的“完整循環”流程,并結合了蝕刻后的結果。與其將 ILT 誤差函數基于抗蝕劑曝光/顯影輪廓的計算模型,不如從最終蝕刻材料圖像模型中導出成本函數,如下圖所示。

(DOM:掩模尺寸;ADI:光刻膠顯影后檢測;AEI:蝕刻后檢測)

為蝕刻工藝構建“數字孿生”模型需要付出巨大努力。然而,全面的掩膜數據到工藝流程優化的好處將是巨大的。

總結

ILT 顯然將擴展到其當前(以內存為中心的)應用程序之外。業界努力支持高效和全面的曲線數據表示標準——包括掩模和設計數據——將有助于加速相應的 EDA 和制造設備的啟用。正如丹平所說,“這不是是否使用ILT的問題,而是何時使用ILT以及使用多少層的問題。”

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。