lattice 文章 進入lattice技術社區

實驗19:步進電機1

- 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握步進電機的原理和設計方法;(3)學習用Verilog HDL描述一個步進電機電路。實驗任務本實驗的任務是設計控制四相繞組的步進電機電機正轉、反轉、停止的控制電路。要求如下:電機運轉規律為:正轉30s→停10s→反轉30s→停10s→正轉30s……實驗原理步進電機是將電脈沖信號轉變為角位移或線位移的開環控制元步進電機件。當電流流過定子繞組時,定子繞組產生一矢量磁場。該磁場會帶動轉子旋轉一角度,使得轉

- 關鍵字: 步進電機 FPGA Lattice Diamond Verilog HDL

實驗18:秒表計數器

- 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握計數器原理;(3)掌握用Verilog HDL數據流和行為級描述寄存器單元的方法。實驗任務設計簡單秒表(60進制),并要求帶啟動、復位、暫停功能。實驗原理如下所示,秒表(60進制)即顯示從00到59循環跳轉計數。并且通過開關設置,達到復位至00,任意時刻暫停和啟動的功能。我們通過將開發板的12M晶振分頻(參考分頻程序)出1Hz的計時頻率,實現秒鐘的效果。將clk_1s的上升沿作為觸發信號計時。通過

- 關鍵字: 秒表計數器 FPGA Lattice Diamond Verilog HDL

實驗17:分頻器

- 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握分頻器原理;(3)學習用Verilog HDL行為級描述時序邏輯電路。實驗任務設計一個任意整數分頻器。實驗原理時鐘信號的處理是FPGA的特色之一,因此分頻器也是FPGA設計中使用頻率非常高的基本設計之一。一般在FPGA中都有集成的鎖相環可以實現各種時鐘的分頻和倍頻設計,但是通過語言設計進行時鐘分頻是最基本的訓練,在對時鐘要求不高的設計時也能節省鎖相環資源。在本實驗中我們將實現任意整數的分頻器,分頻

- 關鍵字: 分頻器 FPGA Lattice Diamond Verilog HDL

實驗16:扭環形計數器

- 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握扭環形計數器原理;(3)學習用Verilog HDL行為級描述時序邏輯電路。實驗任務設計一個右移扭環形計數器。實驗原理將移位寄存器的輸出非q0連接到觸發器q3的輸入,這樣就構成了一個扭環形計數器。初始化復位時,給q0一個初值0000,則在循環過程中依次為:000010001100111011110111001100010000。Verilog HDL建模描述用行為級描述右移扭環形計數器程序清單tw

- 關鍵字: 扭環形計數器 FPGA Lattice Diamond Verilog HDL

實驗15:環形計數器

- 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握環形計數器原理;(3)學習用Verilog HDL行為級描述時序邏輯電路。實驗任務設計一個4位右循環一個1的環形計數器。實驗原理將移位寄存器的輸出q0連接到觸發器q3的輸入,并且在這4個觸發器中只有一個輸出為1,另外3個為0,這樣就構成了一個環形計數器。初始化復位時,給q0一個置位信號,則唯一的1將在環形計數器中循環移位,每4個時鐘同期輸出一個高電平脈沖。Verilog HDL建模描述用行為級描述

- 關鍵字: 環形計數器 FPGA Lattice Diamond Verilog HDL

實驗14:移位寄存器

- 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握移位寄存器原理;(3)學習用Verilog HDL行為級描述時序邏輯電路。實驗任務本實驗的任務是設計一個7位右移并行輸入、串行輸出的移位寄存器。實驗原理如果將多個觸發器級聯就構成一個多位的移位寄存器,如下圖所示,是以4位移位寄存器為例的邏輯電路圖,其中的LD/SHIFT是一個置數/移位控制信號。當LD/SHIFT為1時,在CP作用下,從輸入端A、B、C、D并行接收數據;當LD/SHIFT為0時,在

- 關鍵字: 移位寄存器 FPGA Lattice Diamond Verilog HDL

實驗13:JK觸發器

- 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握JK觸發器原理;(3)學習用Verilog HDL語言行為機描述方法描述JK觸發器電路。實驗任務本實驗的任務是設計一個JK觸發器實驗原理帶使能端RS鎖存器的輸入端R=S=1時,鎖存器的次態不確定,這一因素限制了其應用。為了解決這個問題,根據雙穩態元件兩個輸出端互補的特點,用Q和非Q反饋控制輸入信號,并用J代替S,用K代替R,構成了J-K鎖存器。Verilog HDL建模描述用行為級描述實現的帶異步

- 關鍵字: JK觸發器 FPGA Lattice Diamond Verilog HDL

實驗12:邊沿觸發的D觸發器

- 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握D觸發器原理;(3)學習用Verilog HDL語言行為機描述方法描述D觸發器電路。實驗任務本實驗的任務是描述一個帶有邊沿觸發的同步D觸發器電路,并通過STEP FPGA開發板的12MHz晶振作為觸發器時鐘信號clk,撥碼開關的狀態作為觸發器輸入信號d,觸發器的輸出信號q和~q,用來分別驅動開發板上的LED,在clk上升沿的驅動下,當撥碼開關狀態變化時LED狀態發生相應變化。實驗原理從D觸發器的特

- 關鍵字: D觸發器 FPGA Lattice Diamond Verilog HDL

實驗11:RS觸發器

- 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握RS觸發器原理;(3)學習用Verilog HDL語言行為級描述方法描述RS觸發器電路。實驗任務本實驗的任務是描述一個RS觸發器電路,并通過STEP FPGA開發板的12MHz晶振作為觸發器時鐘信號clk,撥碼開關的狀態作為觸發器輸入信號S,R,觸發器的輸出信號Q和非Q,用來分別驅動開發板上的LED,在clk上升沿的驅動下,當撥碼開關狀態變化時LED狀態發生相應變化。實驗原理基本RS觸發器可以由兩

- 關鍵字: RS觸發器 FPGA Lattice Diamond Verilog HDL

實驗10:七段數碼管

- 1. 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握數碼管驅動;(3)學習用Verilog HDL描述數碼管驅動電路。2. 實驗任務在數碼管上顯示數字。3. 實驗原理數碼管是工程設計中使用很廣的一種顯示輸出器件。一個7段數碼管(如果包括右下的小點可以認為是8段)分別由a、b、c、d、e、f、g位段和表示小數點的dp位段組成。實際是由8個LED燈組成的,控制每個LED的點亮或熄滅實現數字顯示。通常數碼管分為共陽極數碼管和共陰極數碼管,結構如下圖

- 關鍵字: 七段數碼管 FPGA Lattice Diamond Verilog HDL

萊迪思推出Lattice Insights培訓網站,助力FPGA應用設計和開發

- 萊迪思半導體公司,低功耗可編程器件的領先供應商,今日宣布推出官方培訓門戶網站“Lattice Insights?”,幫助客戶和合作伙伴充分體驗低功耗FPGA設計。Lattice Insights由FPGA和培訓專家開發,提供各種學習計劃、強大的課程庫以及可定制的交互式講師指導培訓,涵蓋FPGA開發的方方面面,包括芯片、軟件、解決方案、開發板等。萊迪思全球銷售高級副總裁Mark Nelson表示:“Lattice Insights旨在為我們的客戶提供全面的內容和實踐培訓,幫助他們擴展專業知識,并將先進的解決

- 關鍵字: 萊迪思 Lattice Insights FPGA

富昌電子為萊迪思新FPGA平臺Lattice Avant?提供工程支持

- 中國上海 – 全球知名的電子元器件分銷商富昌電子榮獲萊迪思半導體授予的 2022 年度最佳合作伙伴獎,并且很高興將其專業工程支持擴展到涵蓋萊迪思半導體的全新中端現場可編程門陣列 (FPGA) 平臺 Lattice Avant?。Lattice Avant? 為通信、計算、工業和汽車市場等客戶應用提供出色的能效、先進的連接和優化的計算功能。?與競品相比,Lattice Avant? 幫助客戶在其設計中獲得性能優勢,使功耗最多降低 2.5 倍,吞吐量提高 2 倍(25 Gbps SERDES),封裝

- 關鍵字: 富昌電子 萊迪思 FPGA平臺 Lattice Avant

一個Lattice實習生的內心讀白

- 首先,介紹一下我的個人背景。本科畢業于江蘇省某普通一本院校,期間因為參加過一些競賽,也獲得一些獎項,然后被保送到上海某211高校繼續攻讀碩士研究生。對于FPGA,說會也不算是會,說不會吧,也了解那么一些東西。之前接觸的基本都是Altera的Cyclone系列,本科期間做過兩個簡單的小項目:一個是等精度數字頻率計(說白了就是兩個計數器加D觸發器,用電路都能搭出來);另一個是我的畢業設計,其中用FPGA來驅動CCD和高速ADC的,同時用FPGA實現了一個FIFO,作為ADC與MCU之間數據緩沖(當時因為各

- 關鍵字: Lattice

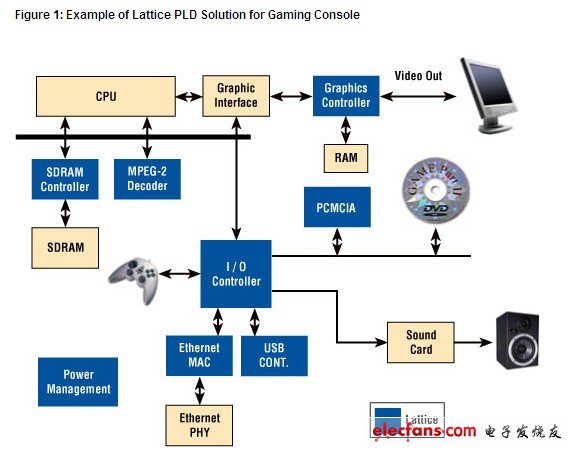

lattice介紹

萊迪思(Lattice)半導體公司提供業界最廣范圍的現場可編程門陣列(FPGA)、可編程邏輯器件(PLD)及其相關軟件,包括現場可編程系統芯片(FPSC)、復雜的可編程邏輯器件(CPLD),可編程混合信號產品(ispPAC?)和可編程數字互連器件(ispGDX?)。萊迪思還提供業界領先的SERDES產品。 FPGA和PLD是廣泛使用的半導體元件,最終用戶可以將其配置成特定的邏輯電路,從而縮短設 [ 查看詳細 ]