異步FIFO是一種在電子系統中得到廣泛應用的器件,文中介紹了一種基于FPGA的異步FIFO設計方法。使用這種方法可以設計出高速、高可靠的異步FIFO。

關鍵字:

FPGA FIFO 軟

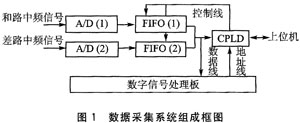

摘要 雷達接收機將雷達回波信號變成中頻信號,數字信號處理系統對中頻信號采樣和處理。本文介紹一種基于A/D和DSP的中頻信號采集技術;給出數據采集系統的原理和框圖,并對A/D與DSP的接口電路進行分析。用FIFO作為兩者之間的接口效果很好;DSP通過CPLD對采樣時序進行控制,可增強系統的靈活性。

關鍵詞 A/D DSP 高速數據采集 FIFO

中頻信號分為和差兩路,高速A/D與DSP組成的數據采集系統要分別對這兩路信號進行采集。對于兩路數據采集電路,A/D與DSP的接口連接是一樣的。兩個A

關鍵字:

A/D DSP 高速數據采集 FIFO

摘要 雷達接收機將雷達回波信號變成中頻信號,數字信號處理系統對中頻信號采樣和處理。本文介紹一種基于A/D和DSP的中頻信號采集技術;給出數據采集系統的原理和框圖,并對A/D與DSP的接口電路進行分析。用FIFO作為兩者之間的接口效果很好;DSP通過CPLD對采樣時序進行控制,可增強系統的靈活性。

關鍵詞 A/D DSP 高速數據采集 FIFO

中頻信號分為和差兩路,高速A/D與DSP組成的數據采集系統要分別對這兩路信號進行采集。對于兩路數據采集電路,A/D與DSP的接口連接是一樣的。兩個A

關鍵字:

A/D DSP 高速數據采集 FIFO

分別基于Hynix公司的SRAM HY64UDl6322A和DRAM HY57V281620E,介紹了采用兩種不同的RAM結構,通過CPLD來設計并實現大容量FIFO的方法。

關鍵字:

SRAM DRAM FIFO 大容量

介紹如何利用FIFO芯片CY7C4255V實現高速高精度模/數轉換器AD767l與LPC2200系列ARM處理器的接口。

關鍵字:

FIFO ARM 處理器 接口

引言 射頻定時發送器是射頻控制模塊中的一個重要組成部分,用于產生需要定時發送的射頻控制信號:AD_ON(模數轉換信號)、DA_ON(數模轉換信號)、APC(自動功率控制信號)、AGC(自動增益控制信號)和AFC(自動頻率控制信號),再通過選擇兩個SPI接口RF_SPI和AD_SPI把控制信號定時地傳送到射頻發送模塊。射頻定時發送器需要完成的四種基本功能分別是:定時發送、競爭發送、數據采樣時鐘分頻,以及APC_burst模式,如圖1所示,本文將詳細闡述這些基本功能模塊的設計原理。

關鍵字:

嵌入式系統 單片機 射頻 定時發送器 FIFO 測試工具

基于FPGA的IPV6數據包的拆裝實現 王志遠, 杜詩武, 曲 晶(信息工程學院 信息技術研究所,河南 鄭州 450002) 摘 要:介紹了一種運用FPGA將IPV6數據包的包頭和數據部分分離并重新封裝的方法。利用該方法,可以使IPV6數據包的拆裝處理速度達到2Gbit/s以上。 關鍵詞:FPGA IPV6數據包 拆裝 FIFO

筆者在參與國家“863”重大專題項目“高速密碼芯片及驗證平臺系統”的過程中,遇到了將IPV6數據包的包頭和數據部分拆開,然后把數據部分送密碼芯片進行加

關鍵字:

FIFO FPGA IPV6數據包 拆裝

電子產品世界,為電子工程師提供全面的電子產品信息和行業解決方案,是電子工程師的技術中心和交流中心,是電子產品的市場中心,EEPW 20年的品牌歷史,是電子工程師的網絡家園

關鍵字:

MCU 藍牙 CPU FIFO Wi-Fi

本文系統地介紹了一種由數字信號處理器TMS320C6416、可編程邏輯器件Spartan3E構成的高速數據采集系統。

關鍵字:

FPGA FIFO

FT2232C是一款USB到UART/FIFO轉換電路。文中介紹FT2232C的特性、工作原理及應用領域,給出該電路在各種不同場合的典型應用電路。

關鍵字:

2232C FIFO UART

說明了如何使用CY7C4265-10AC FIFO來實現TMS320C6205與AD904AST模數轉換器的接口,詳細介紹了TMS320C6205讀取FIFO中數據的速度以及如何設置EMIF的CExCTL寄存器的接口時序。

關鍵字:

C6000 FIFO 320C

摘 要:本文介紹了一種基于PCI總線的高速實時數據采集系統的設計與實現方法,主要討論了高速數據采集的存儲與傳輸的硬件解決方案,以及該系統的控制邏輯的實現,最后給出了控制邏輯仿真波形。關鍵詞:PCI總線;CPCI總線;高速實時數據采集;FIFO;CPLD

引言目前的大多數雷達信號處理機都是采用自定義總線,不具有通用性,每進行一些系統功能的改變就需要大量的硬件改動。而CPCI總線作為一種新興的工業總線,其采用了PCI總線的電氣特性以及VME總線的物理特性,兼具了二者的優點

關鍵字:

CPCI總線 CPLD FIFO PCI總線 高速實時數據采集

首先介紹異步FIFO的概念、應用及其結構,然后分析實現異步FIFO的難點問題及其解決辦法;在傳統設計的基礎上提出一種新穎的電路結構并對其進行綜合仿真和FPGA實現。

關鍵字:

FIFO FPGA

在采用CCD對非透明薄板厚度的測量系統設計中,采用高速A/D和DSP等器件進行電路設計可以確定CCD的像點位置。

關鍵字:

之間 接口 DSP A/D 設計 FIFO

fifo介紹

采用FIFO方式時,信息被以所收到的次序進行傳輸。

表示信息存儲的一種數據結構,含義是先進入的對象先取出。隊列(Queue )就是基于這種性質實現的。

FIFO( First In First Out)簡單說就是指先進先出。由于微電子技術的飛速發展,新一代FIFO芯片容量越來越大,體積越來越小,價格越來越便宜。作為一種新型大規模集成電路,FIFO芯片以其靈活、方便、高效的特性,逐漸在高速數據采 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473