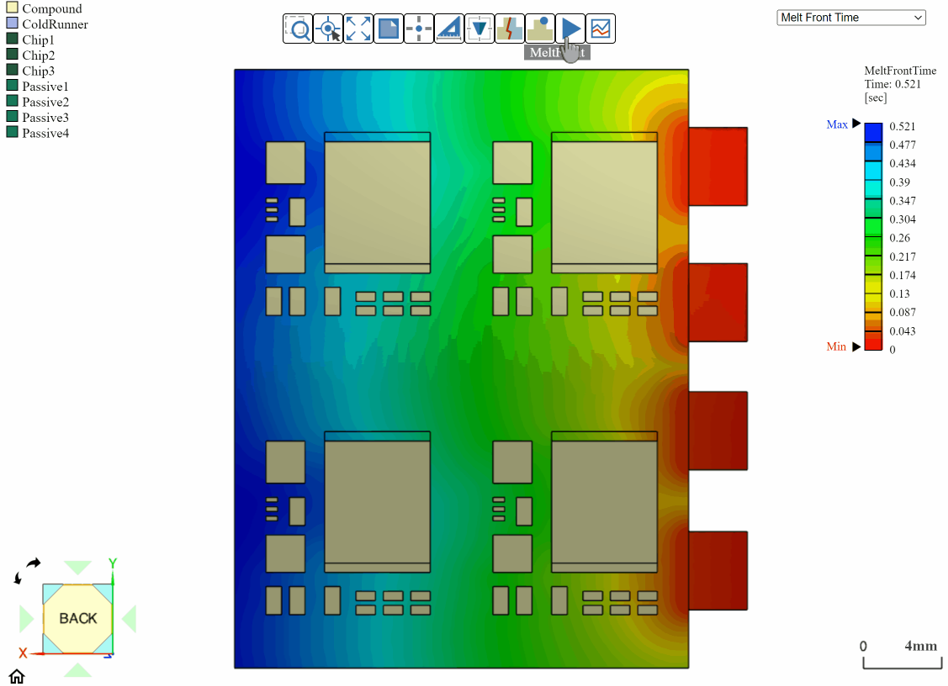

- 在IC封裝制程的制程模擬中,為了同時提升工作效率與質量,CAE團隊常會面臨到許多挑戰。在一般的CAE分析流程中,仿真分析產生結構性網格,是非常繁瑣且相當花時間的。必須要先匯入2D (或3D) 圖檔,接著陸續建立表面網格、高質量的三維實體網格,再檢查其網格的質量及正確性,以確保沒有網格缺陷;接著再設定不同的屬性,如chip, die等等;完成一個單元 (unit) 的實體網格建立后,還需要根據 strip 的設計并透過復制實體網格等方式建立一個完整封裝模型,并且在模型外進行流道等實體網格的建立及邊界條件設定

- 關鍵字:

IC封裝仿真分析 科盛科技

ic封裝仿真分析介紹

您好,目前還沒有人創建詞條ic封裝仿真分析!

歡迎您創建該詞條,闡述對ic封裝仿真分析的理解,并與今后在此搜索ic封裝仿真分析的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473