- 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握D觸發器原理;(3)學習用Verilog HDL語言行為機描述方法描述D觸發器電路。實驗任務本實驗的任務是描述一個帶有邊沿觸發的同步D觸發器電路,并通過STEP FPGA開發板的12MHz晶振作為觸發器時鐘信號clk,撥碼開關的狀態作為觸發器輸入信號d,觸發器的輸出信號q和~q,用來分別驅動開發板上的LED,在clk上升沿的驅動下,當撥碼開關狀態變化時LED狀態發生相應變化。實驗原理從D觸發器的特

- 關鍵字:

D觸發器 FPGA Lattice Diamond Verilog HDL

- 我們的設計需要多大容量的芯片?我們的設計能跑多快?這是經常困擾工程師的兩個問題。對于前一個問題,我們可能還能先以一個比較大的芯片實現原型,待原型完成再選用大小合適的芯片實現。對于后者,我們需要一個比較精確的預估。

- 關鍵字:

頻率計算 D觸發器 FPGA Tlogic

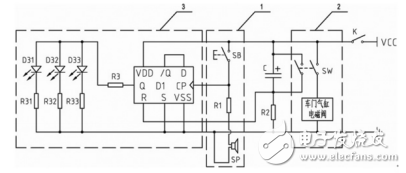

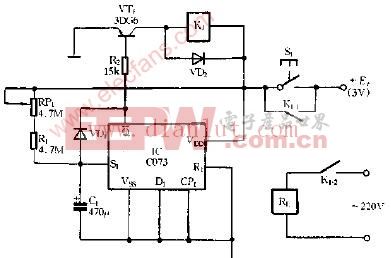

- 圖中所示是用CMOS電路D觸發器組成的觸摸式反轉開關。圖中在CL端與觸摸點K之間加入了一個或非門組成的單穩態觸發器,它將手指觸摸時送進來的電壓,展寬成一個固定寬度...

- 關鍵字:

D觸發器 組成觸摸式 反轉開關

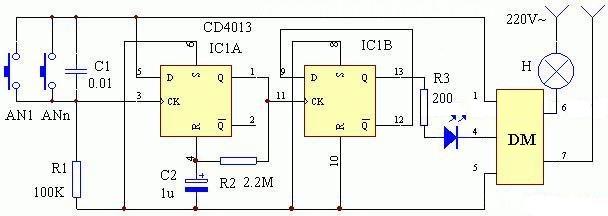

- 從D觸發器的真值表可知,當時鐘脈沖CL=1時,數據輸入端D的狀態會被“置放”入觸發器中去,而與觸發器原狀無關。如果當時鐘沖CL=1,D端狀態不旋轉放入觸發器中...

- 關鍵字:

D觸發器 信號電路圖

- //基本D觸發器 module D_EF(Q,D,CLK) input D,CLK; output Q; reg Q; //在always語句中被賦值的信號要聲明為reg類型 寄存器定義 always @ (posedge CLK) //上升沿,下降沿用negedge表示,^_^ 需要記憶 begin Q <= D; end endm

- 關鍵字:

D觸發器 Verilog

- 導讀:觸發器又稱為雙穩態多諧振蕩器,是一種可以存儲電路狀態的電子元件,廣泛用于運算器、計算器、存儲器中。最簡單的觸發器便是RS觸發器了,相信大家都有所了解,今天在此基礎上,我們一起來八一八D觸發器原理的真相。

一、D觸發器原理- -簡介

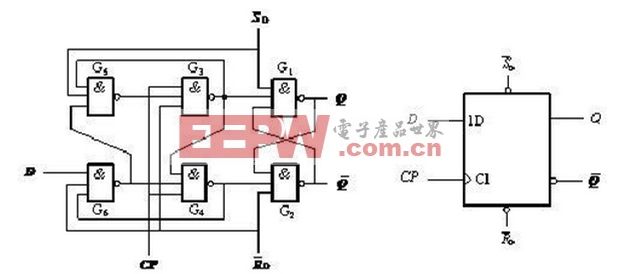

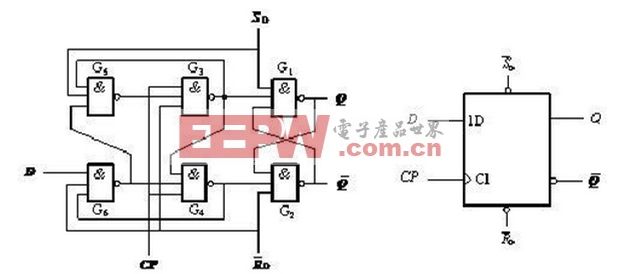

D觸發器(data flip-flop)也稱為維持-阻塞邊沿D觸發器,由六個與非門組成,其電路圖及其邏輯符號如下圖所示。其中G1和G2構成基本的RS觸發器,G3和G4構成時鐘控制電路,G5和G6組成數據輸入電路。由于 分別為復位端和置位端,在分析D觸發器工作原

- 關鍵字:

D觸發器 D觸發器原理

- 入門前

剛才開始接觸邏輯設計很多人會覺得很簡單:因為verilog的語法不多,半天就可以把書看完了。但是很快許多人就發現這個想法是錯誤的,他們經常埋怨綜合器怎么和自己的想法差別這么大:它竟然連用for循環寫的一個計數器都不認識!

相信上一段的經歷大部分人都曾有,原因是做邏輯設計的思維和做軟件的很不相同,我們需要從電路的角度去考慮問題。

在這個過程中首先要明白的是軟件設計和邏輯設計的不同,并理解什么是硬件意識。

軟件代碼的執行是一個順序的過程,編繹以后的機器碼放在存儲器里,等著C

- 關鍵字:

邏輯設計 verilog D觸發器

d觸發器介紹

邊沿D 觸發器:

負跳沿觸發的主從觸發器工作時,必須在正跳沿前加入輸入信號。如果在CP 高電平期間輸入端出現干擾信號,那么就有可能使觸發器的狀態出錯。而邊沿觸發器允許在CP 觸發沿來到前一瞬間加入輸入信號。這樣,輸入端受干擾的時間大大縮短,受干擾的可能性就降低了。邊沿D觸發器也稱為維持-阻塞邊沿D觸發器。

電路結構: 該觸發器由6個與非門組成,其中G1和G2構成基本RS觸發器。

[

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473