- 基于0.13微米CMOS工藝下平臺式FPGA中可重構RAM模塊的一種設計方法,1. 引言

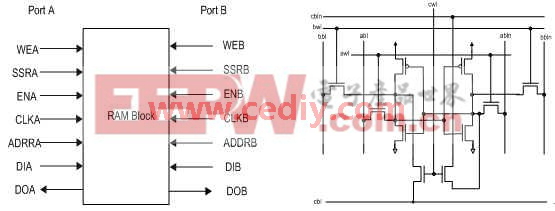

對于需要大的片上存儲器的各種不同的應用,FPGA 需要提供可重構且可串聯的存儲器陣列。通過不同的配置選擇,嵌入式存儲器陣列可以被合并從而達到位寬或字深的擴展并且可以作為單端口,雙端口

- 關鍵字:

RAM 重構 模塊 設計 方法 FPGA 平臺 0.13 微米 CMOS 工藝

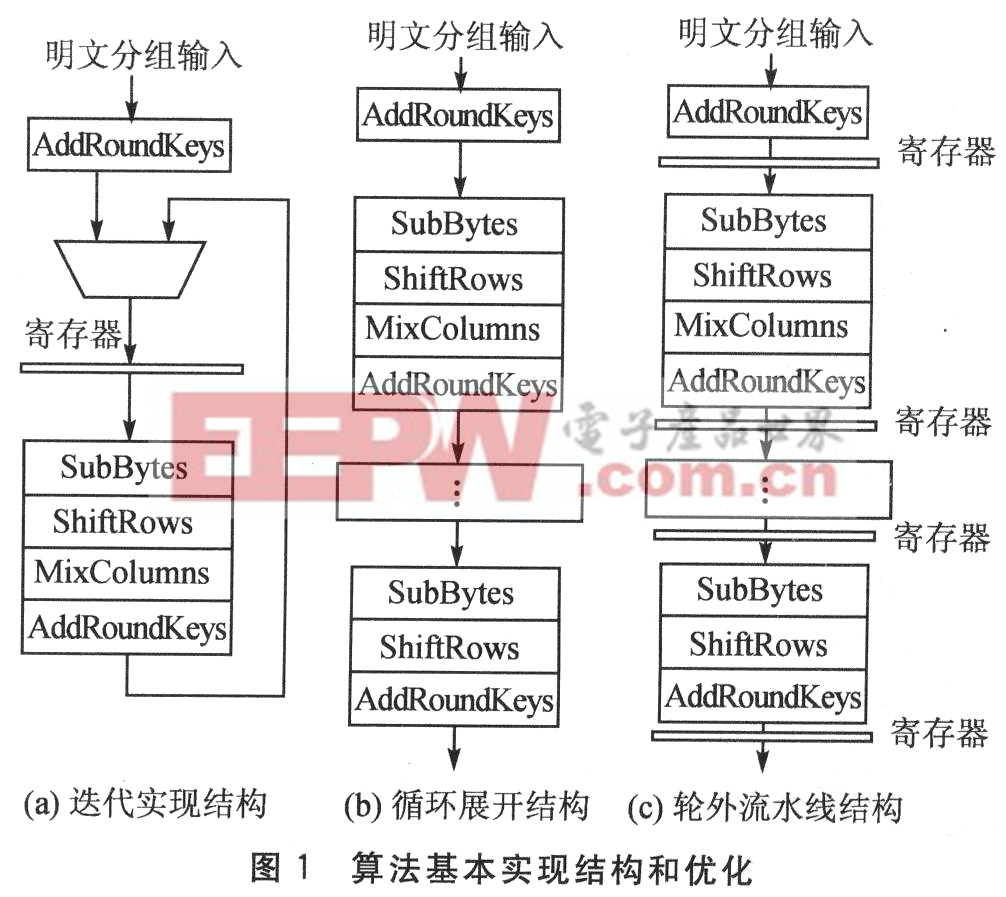

- 摘要 AES-Rijndael算法是美國取代DES的新一代分組加密算法標準,也是事實上的國際標準。本文在可重構平臺上針對 128位密鑰長度AES算法的流水線性能優化技術進行了研究,通過對基本運算優化、循環展開、輪內流水線、輪

- 關鍵字:

性能 優化 流水線 算法 平臺 AES 重構

重構介紹

重構 重構的定義

重構(名詞):對軟件內部結構的一種調整,目的是在不改變"軟件之可察行為"前提下,提高其可理解性,降低其修改成本.

重構(動詞):使用一系列重構準則(手法),在不改變"軟件之可察行為"前提下,調整其結構.

兩種定義都強調是在不改變"軟件的外部行為"前提下,不改變"軟件之可察行為"就是說讓修改不影響外部使用程序(程序員),在個外部來看,程序的行為和結果沒有任何的變 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473