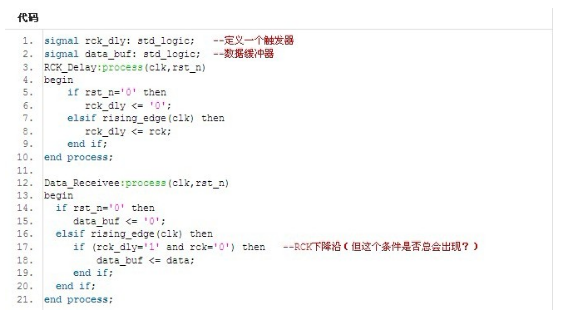

- 在同步電路設計中,邊沿檢測是必不可少的! 例如:在一個時鐘頻率16MHz的同步串行總線接收電路里,串行總線波特率為1Mbps。在串行總線的發送端是在同步時鐘(1MHz)的上升沿輸出數據,在接收端在同步時鐘的下降沿對輸入數據進行接收采樣。在這個接收電路里檢測同步時鐘的下降沿是必不可少的。假設主時鐘-clk,同步時鐘-rck,同步數據-data。 有些人在邊沿檢測的時候就喜歡這樣做:

但是大家忽略了一種情況,就是clk與rck之間比沒有必然的同步關系,當r

- 關鍵字:

FPGA 邊沿檢測

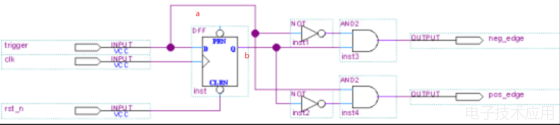

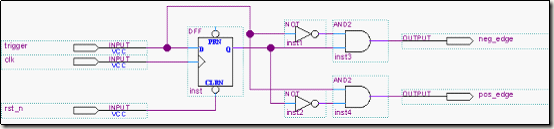

- 1、所謂邊沿檢測,就是檢測輸入信號或FPGA內部邏輯信號電平的跳變,即實現上升沿或下降沿的檢測,捕獲到以后以此用作使能信號(簡單可理解為:一旦檢測到這個信號,則發生什么什么),來作為時序邏輯的觸發信號。總之,在基礎中,這個還是很重要的,在后面的串口和SPI接口中都要用到。 (一)、一級寄存器

從一級寄存器中很好理解下降沿和上升沿的檢測:a和b都是從trigger來的(三者一樣),只是b比a在時間上遲了一個寄存器的時間。現在假設0時刻到了,trigger到

- 關鍵字:

邊沿檢測 寄存器

- 一、為什么要講邊沿檢測

也許,沒有那么一本教科書,會說到這個重要的思想;也許,學了很久的你,有可能不知道這個重要的思想吧。很慚愧,我也是在當年學了1年后才領悟到這個思想的。

說實話,我的成長很艱辛,沒有人能給我系統的指導,而我得撐起這一片藍天,于是乎無數個漏洞,我一直在修補我的不足。我沒能對自己滿足過,不是說我“貪得無厭”,而是,我不夠“完美”。人可以不完美,但不可以不追求完美;或許終點永遠達不到,但努力的過程,你一直在靠近完美;有方向感地奮

- 關鍵字:

FPGA 邊沿檢測

邊沿檢測介紹

您好,目前還沒有人創建詞條邊沿檢測!

歡迎您創建該詞條,闡述對邊沿檢測的理解,并與今后在此搜索邊沿檢測的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473