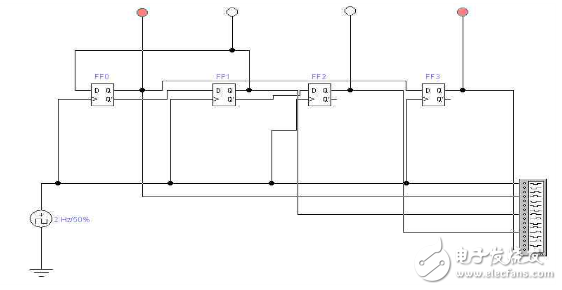

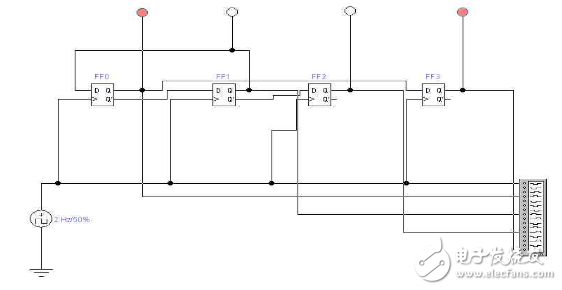

- 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握環形計數器原理;(3)學習用Verilog HDL行為級描述時序邏輯電路。實驗任務設計一個4位右循環一個1的環形計數器。實驗原理將移位寄存器的輸出q0連接到觸發器q3的輸入,并且在這4個觸發器中只有一個輸出為1,另外3個為0,這樣就構成了一個環形計數器。初始化復位時,給q0一個置位信號,則唯一的1將在環形計數器中循環移位,每4個時鐘同期輸出一個高電平脈沖。Verilog HDL建模描述用行為級描述

- 關鍵字:

環形計數器 FPGA Lattice Diamond Verilog HDL

- 基于探索仿真三態門總線傳輸電路的目的,采用Multisim10仿真軟件對總線連接的三態門分時輪流工作時的波形進行了仿真實驗測試,給出了仿真實驗方案,即用Multisim仿真軟件構成環形計數器產生各個三態門的控制信號、用脈沖信號源產生各個三態門不同輸入數據信號,用Multisim仿真軟件中的邏輯分析儀多蹤同步顯示各個三態門的控制信號、數據輸入信號及總線輸出信號波形,結論是仿真實驗可直觀形象地描述三態門總線傳輸電路的工作特性,所述方法的創新點是解決了三態門的工作波形無法用電子實驗儀器進行分析驗證的問題。

- 關鍵字:

三態門 總線傳輸 環形計數器 邏輯分析儀

環形計數器介紹

您好,目前還沒有人創建詞條環形計數器!

歡迎您創建該詞條,闡述對環形計數器的理解,并與今后在此搜索環形計數器的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473