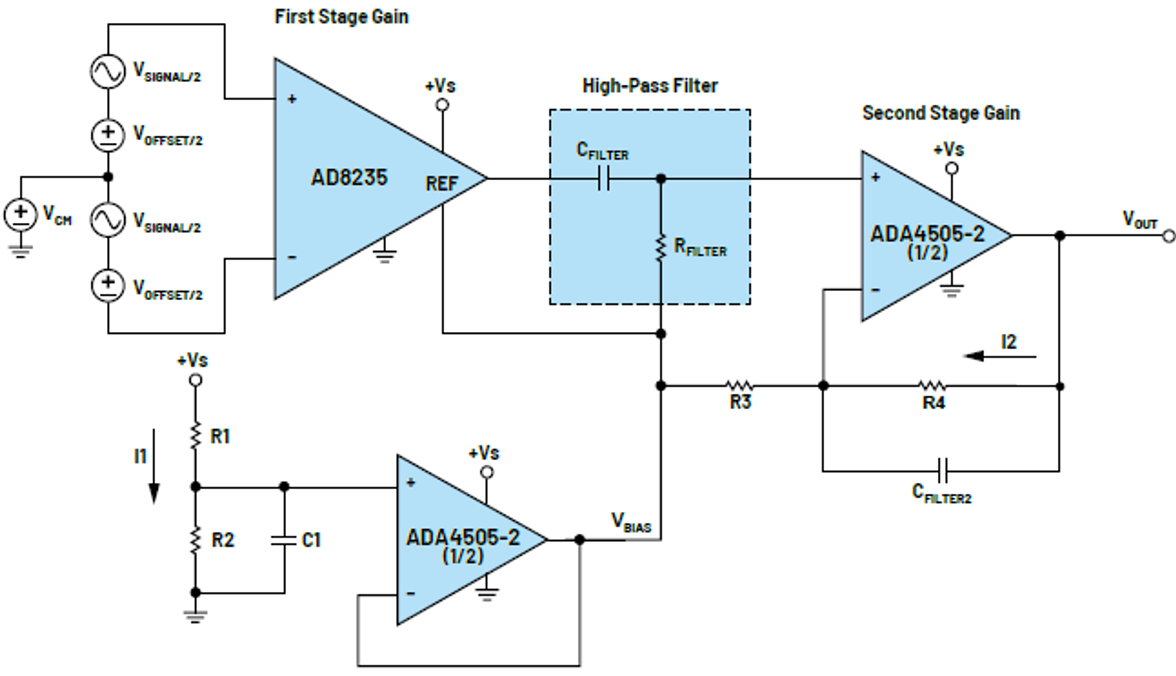

- 摘要本文將介紹低功耗系統在降低功耗的同時保持精度所涉及的時序因素和解決方案,以滿足測量和監控應用的要求。文中將說明當所選ADC是逐次逼近寄存器(SAR) ADC時的時序影響因素。Σ-Δ架構的時序考慮因素有所不同(參見本系列文章的上篇)。本文探討信號鏈在模擬前端時序、ADC時序和數字接口時序方面的考慮。?模擬前端時序考量圖1中的三個模塊可以分別予以考慮,從模擬前端(AFE)開始。信號鏈的類型會改變AFE,但有一些共同方面適用于大多數電路。圖1.使用多路復用SAR ADC的AFE時序考量?

- 關鍵字:

精密信號鏈 時序因素 ADI

時序因素介紹

您好,目前還沒有人創建詞條時序因素!

歡迎您創建該詞條,闡述對時序因素的理解,并與今后在此搜索時序因素的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473