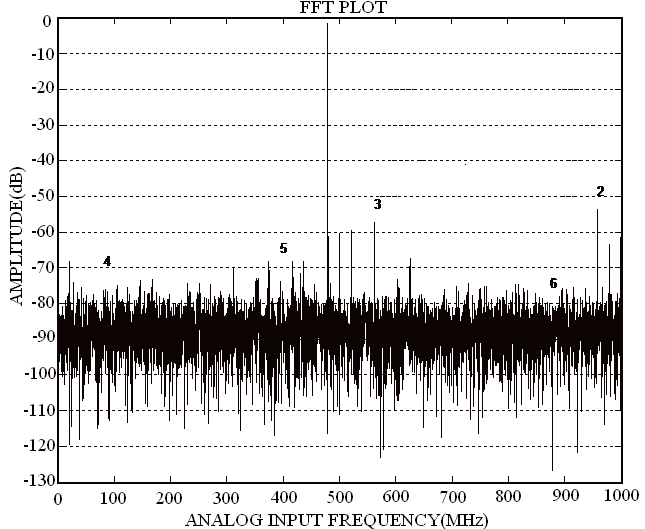

- 本文提出了一種基于0.18 μm BiCMOS工藝設計的開環采樣保持電路,采用了增益和失調誤差數字校準算法提升動態性能,應用于高速折疊/插值型ADC中。電路仿真和測試結果表明,在2GSPS采樣率下,折疊/插值型ADC的DNL≤±0.3LSB、INL≤±0.3LSB,有效位達到7.32位。

- 關鍵字:

開環采樣保持電路 數字校準 折疊插值 202205

- 摘要:數字校準是高速高精度流水線ADC設計中的關鍵技術之一。文章提出了一種可通過校準控制生成測試信號,自動計算權重來對流水線ADC中電容失配進行誤差補償的技術。該技術能有效地減小增益有限、電荷注入等非理想因

- 關鍵字:

流水線ADC 數字校準 非線性誤差

數字校準介紹

您好,目前還沒有人創建詞條數字校準!

歡迎您創建該詞條,闡述對數字校準的理解,并與今后在此搜索數字校準的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473