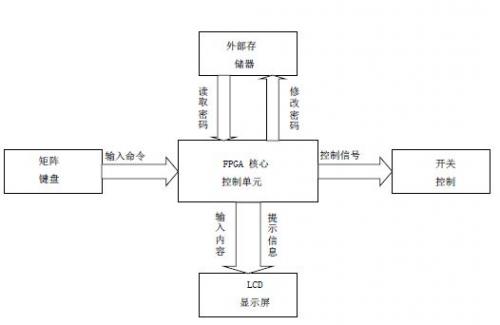

- 本文介紹了一種以FPGA為基礎的數字密碼鎖。采用自頂向下的數字系統設計方法,將數字密碼鎖系統分解為若干子系統,并且進一步細劃為若干模塊,然后用硬件描述語言VHDL來設計這些模塊,同時進行硬件測試。測試結果表明該數字密碼鎖能夠校驗10位十進制數字密碼,且可以預置密碼,設有斷電保護裝置,解碼有效指示等相應功能。

1功能概述

(1)密碼鎖的工作時鐘由外部晶振提供,時鐘頻率為50MHz,運算速度高,工作性能穩定。

(2)密碼的設置和輸入由外接鍵盤完成,控制電路的安全系數高,操作方便;

- 關鍵字:

FPGA 數字密碼鎖

- 摘要:采用VHDL硬件描述語言,以自頂向下的設計方法,在Quartus II 9.1的開發環境下,設計了基于FPGA的數字密碼鎖。并選用ALTERA公司Cylone II系列的EP2C35F672C8芯片為其硬件條件,驗證了其功能及可靠性。結果表明

- 關鍵字:

FGPA 數字密碼鎖

數字密碼鎖介紹

您好,目前還沒有人創建詞條數字密碼鎖!

歡迎您創建該詞條,闡述對數字密碼鎖的理解,并與今后在此搜索數字密碼鎖的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473