- 降低任何嵌入式設計的體積和成本的常用方法是使用具有較少I/O引腳的通信總線。雖然從并行總線發展到串行總線可明顯減小體積和降低成本,但是從一種串行總線發展為另一種具有較少引腳的串行總線也很有用。用串行總,降低任何嵌入式設計的體積和成本的常用方法是使用具有較少I/O引腳的通信總線。雖然從并行總線發展到串行總線可明顯減小體積和降低成本,但是從一種串行總線發展為另一種具有較少引腳的串行總線也很有用。用串行總線替

- 關鍵字:

串行總線 體積 引腳 并行總線

- [導讀] 由于FPGA技術和ARM技術應用越來越廣泛,通過設計并行總線接口來實現兩者之間的數據交換,可以較容易地解 ...

- 關鍵字:

ARM 并行總線 機載雷達

- 摘要:通過EP2C20Q240 器件和LPC2478 處理器,研究ARM 應用系統外部并行總線的工作原理和時序特性,以及在FPGA 中 ...

- 關鍵字:

FPGA ARM 并行總線

- 0 引言在數字系統的設計中,FPGA+ARM 的系統架構得到了越來越廣泛的應用,FPGA 主要實現高速數據的處理;ARM 主要實現系統的流程控制.人機交互.外部通信以及FPGA 控制等功能.I2C.SPI 等串行總線接口只能實現FPGA 和AR

- 關鍵字:

FPGA ARM 并行總線 仿真

- 引 言

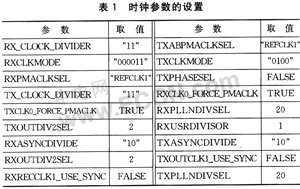

目前,多數計算機、嵌入式處理設備和通信設備都采用并行總線,但隨著芯片性能不斷提升和系統越來越復雜,數據傳輸帶寬已成為提高系統性能的瓶頸。雖然增大并行總線寬度可以提高芯片與芯片之間、背板與背板之間的數據吞吐量,但是數據線的增多和傳輸速率的加快會使PCB布線的難度提高,并且增加了信號延時和時鐘相位偏移。高速串行互連技術成為提高數據傳輸帶寬的有效解決途徑。

新的串行總線技術不斷涌現,如新推出的串行總線標準有PCI-express、RapidI()、10Gigabit Etherne

- 關鍵字:

嵌入式 RocketIO 通信 并行總線 串行總線

并行總線介紹

您好,目前還沒有人創建詞條并行總線!

歡迎您創建該詞條,闡述對并行總線的理解,并與今后在此搜索并行總線的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473