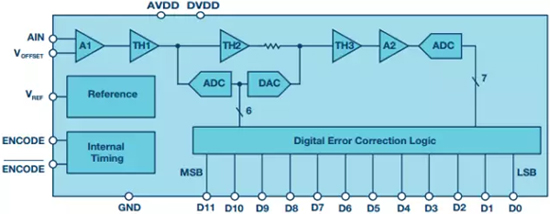

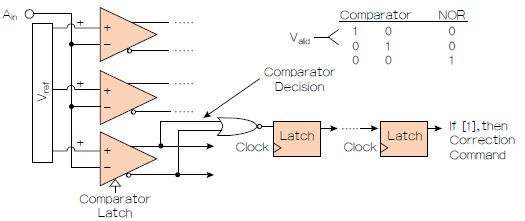

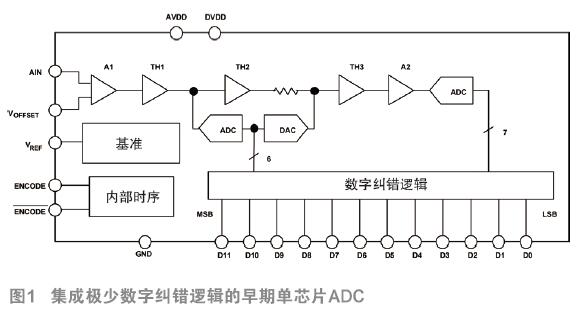

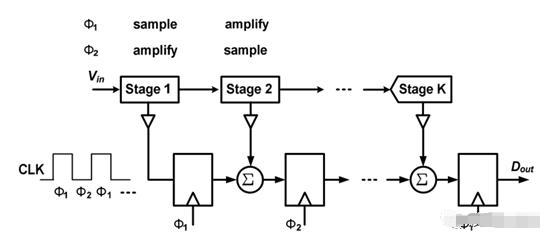

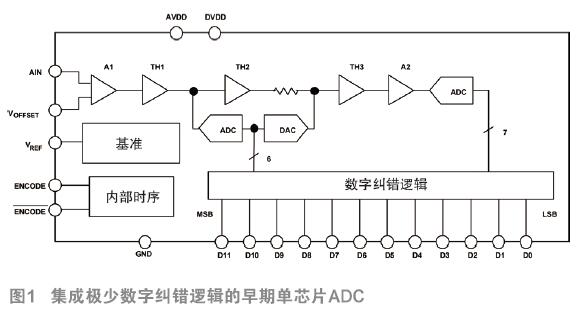

- 數據轉換器充當現實模擬世界與數字世界之間的橋梁已有數十年的歷史。從占用多個機架空間并消耗大量電能(例如DATRAC 11位50kSPS真空管ADC的功耗為500W)的分立元件起步,數據轉換器現已蛻變為高度集成的單芯片IC。從第一款商用數據轉換器誕生以來,對更快數據速率的無止境需求驅動著數據轉換器不斷向前發展。ADC的最新化身是采樣速率達到GHz的RF采樣ADC。 早先的ADC設計使用的數字電路非常少,主要用于糾錯和數字驅動器。新一代GSPS(每秒千兆樣本)轉換器(也稱為RF采樣ADC)利用

- 關鍵字:

ADC RF

- 2016年4月8日-4月10日,春季(第87屆)中國電子展(87nd?China Electronics Fair ) 在深圳會展中心舉行。e2v公司聯合其在中國大陸和香港地區的代理商創佳中國有限公司參加了此次展會。 展會期間,筆者藉此機會訪問了e2v公司CEO Steve Blair先生, e2v亞太區VP Anthony Fernandez先

- 關鍵字:

e2v 創佳中國 中國電子展 ADC

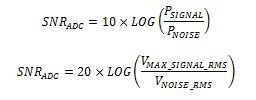

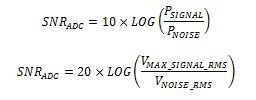

- 看到一片關于AD轉換設計中的基本問題整理博文,特地轉載過來和大家共分享。 了解數據轉換器錯誤及參數 1.如何選擇高速模數轉換之前的信號調理器件;如何解決多路模數轉換的同步問題? ADC之前的信號調理,最根本的原則就是信號調理引起的噪聲和誤差要在ADC的1個LSB之內。根據這個目的,可以需要選擇指標合適的運放。至于多路ADC同步的問題,一般在高速ADC的數據手冊中都會有一章來介紹多片同步問題,你可以看一下里面的介紹。 2.在挑選ADC時如何確定內部噪聲這個參數? 一般ADC都有信噪比SNR或者

- 關鍵字:

ADC 數據轉換器

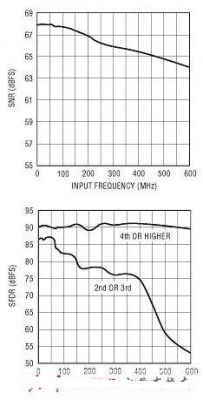

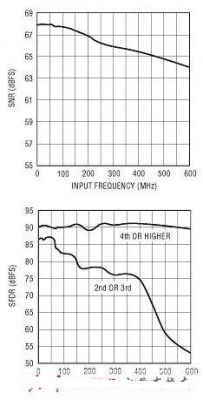

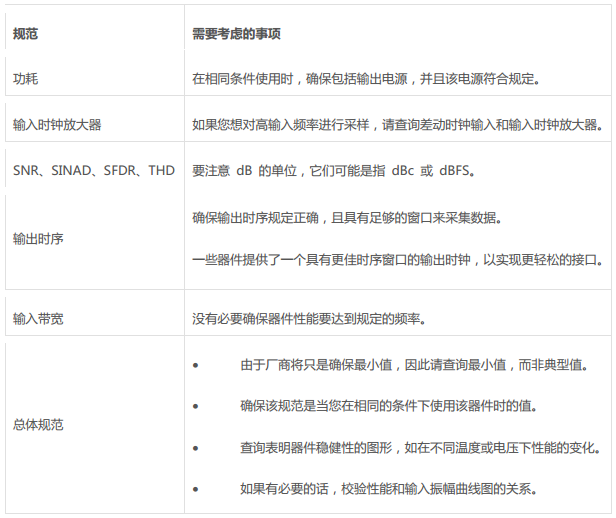

- 高速ADC的性能特性對整個信號處理鏈路的設計影響巨大。系統設計師在考慮ADC對基帶影響的同時,還必須考慮對射頻(RF)和數字電路系統的影響。由于ADC位于模擬和數字區域之間,評價和選擇的責任常常落在系統設計師身上,而系統設計師并不都是ADC專家。

還有一些重要因素用戶在最初選擇高性能ADC時常常忽視。他們可能要等到最初設計樣機將要完成時才能知道所有系統級結果,而此時已不太可能再選擇另外的ADC。

影響很多無線通信系統的重要因素之一就是低輸入信號電平時的失真度。大多數無線傳輸到達ADC的信號

- 關鍵字:

ADC

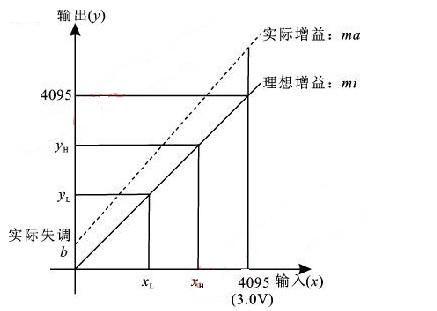

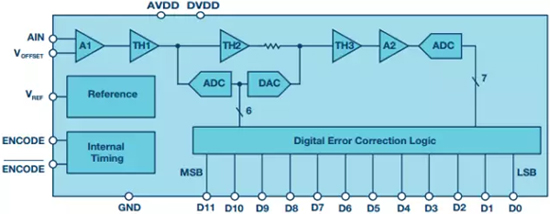

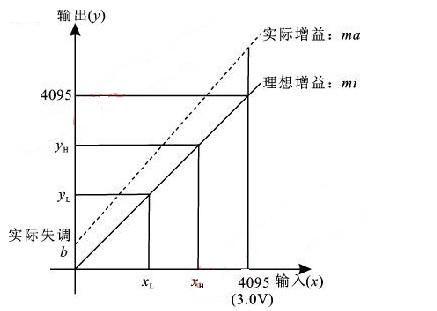

- ADC模塊是一個12位、具有流水線結構的模數轉換器,用于控制回路中的數據采集。本文提出一種用于提高TMS320F2812ADC精度的方法,使得ADC精度得到有效提高。 1 ADC模塊誤差的定義及影響分析 1.1 誤差定義 常用的A/D轉換器主要存在:失調誤差、增益誤差和線性誤差。這里主要討論失調誤差和增益誤差。理想情況下,ADC模塊轉換方程為y=x×mi,式中x=輸入計數值 =輸入電壓×4095/3;y=輸出計數值。在實際中,A/D轉換模塊的各種誤差是不可避免的,這

- 關鍵字:

數字處理器 ADC

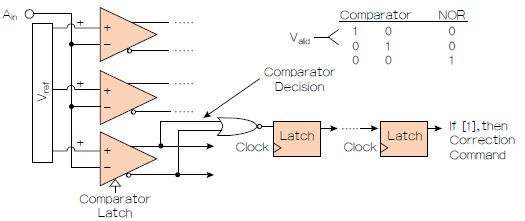

- 高速模數轉換器(ADC)存在一些固有限制,使其偶爾會在其正常功能以外產生罕見的轉換錯誤。但是,很多實際采樣系統不容許存在高ADC轉換誤差率。因此,量化高速模數轉換誤差率(CER)的頻率和幅度非常重要。 高速或GSPS ADC(每秒千兆采樣ADC)相對稀疏出現的轉換錯誤不僅造成其難以檢測,而且還使測量過程非常耗時。該持續時間通常超出毫秒范圍,達到幾小時、幾天、幾周甚至是幾個月。為了幫助消減這一耗時測試負擔,可以在一定“置信度”的確定性情況下估算誤差率,而仍然保持結果的質量。 誤碼率(BER

- 關鍵字:

ADC CER

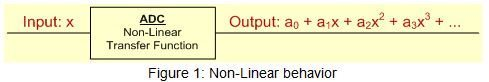

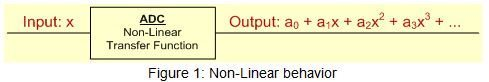

- 我們繼續講解與逐次逼近寄存器 (SAR) 數模轉換器 (ADC) 輸入類型有關的內容。在之前的部分中,我研究了輸入注意事項和SAR ADC之間的性能比較。在這篇帖子中,我們將看一看造成SAR ADC內總諧波失真 (THD) 的源頭,以及他在不同的輸入類型間有什么不一樣的地方 THD影響 讓我們首先看看諧波失真是如何被引入的。本質上來說,轉換器是一個非線性系統。如果系統完全線性,輸入“x”將在輸出上以線性的形式表現為“m

- 關鍵字:

SAR ADC

- 在選擇一個SAR ADC時所考慮的某些關鍵技術規格包括分辨率、通道數量、采樣率、電源范圍、功耗、數字接口和時鐘速度。但是諸如信噪比 (SNR) 和總諧波失真 (THD) 的噪聲和AC參數是怎樣的呢?這些參數會影響總體系統性能,并因此影響到SAR輸入類型的選擇。 噪聲影響 單端輸入:這些SAR只需要一條導線/電纜和一個單輸入驅動器,如果有的話,連接至電源。需要注意的是,這些ADC測量相對于SAR自身接地的輸入信號。雖然這是最簡單的配置,信號接地和SA

- 關鍵字:

SAR ADC

- 本文主要介紹了ADC和DAC常用的56個技術術語,如“采集時間”、“混疊”、“孔徑延遲”等,幫助初學者更好的理解專業術語。 采集時間 采集時間是從釋放保持狀態(由采樣-保持輸入電路執行)到采樣電容電壓穩定至新輸入值的1 LSB范圍之內所需要的時間。采集時間(Tacq)的公式如下:

混疊 根據采樣定理,超過奈奎斯特頻率的輸入信號頻率為“混疊”頻率。也就是說,這些頻率被“折疊”或復制到奈奎斯特頻率附近的其它頻譜位置。為防止混疊,必須對所有有害信

- 關鍵字:

ADC DAC

- 數據轉換器現已蛻變為高度集成的單芯片IC。從第一款商用數據轉換器誕生以來,對更快數據速率的無止境需求驅動著數據轉換器不斷向前發展。目前ADC的最新產品是采樣速率達到GHz的RF采樣ADC。更高帶寬的需求伴隨著更高容量的需求,這就給FPGA I/O帶來了更大的壓力,而RF采樣ADC可以利用內部DDC予以化解。

- 關鍵字:

ADC RF采樣 GHz 201603

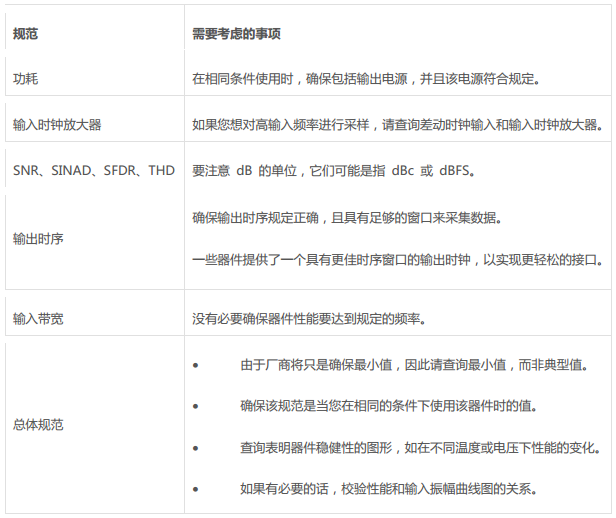

- 和一個產品的任何其他方面一樣,產品說明書也可以得到不斷的改進,廠商正努力地詳細闡明產品說明書1。然而,市場上已經遺留了許多產品/產品說明書版本,對新版本或者更早的版本來說,不同標準的采用也取決于不同的因素。即使有一些特定的標準已經公開發表(如參考書目 2 所提到的),標準的統一仍然是遙遙無期。 本文的目的就在于突出不同廠商或同一廠商在為不同的高速模數轉換器 (ADC) 撰寫產品說明書時所采用的標準之間的差異。表 1 是選擇正確器件時可以使用

- 關鍵字:

TI ADC

- 最近幾年,高速、高精度的模數轉換器變得疾速。在 2006 年,一款業界一流的 12-位轉換器才達到 250 兆采樣/秒 (MSPS)。而今天,這一速度已經翻了一番,達到了 500 MSPS。14-位和 16-位精度的類似發展趨勢也日益明顯。這表明,在比特精度不變的條件下,ADC 速度正以幾乎每年翻一番的速度發展。采樣速率增長的結果是,收斂數字時序來確保您終端系統的數據完整性正變得越來越重要。 要收斂時

- 關鍵字:

ADC

- 在您開始設計以前,首先要看一下您想要數字化的信號類型。例如,如果您知道系統所有通道的最高、最低頻率以及精度要求,那么您可能會需要數個 ADC。 另一種情況下,這些通道可能具有互不相同的時間關系,這就要求一種能夠保護相位信息的同時采樣方法。您可以利用采樣保持電路和一個 ADC 來達到這一目的,而使用獨立的 ADC 可能會更容易一些。 圖 1 顯示了一個 Δ-Σ 轉換器多路復用電路,在該多路復用器的信號端上有一些

- 關鍵字:

轉換器 ADC

- 本文給大家分享了ADC學習知識。

過采樣頻率:增加一位分辨率或每減小6dB 的噪聲,需要以4 倍的采樣頻率fs 進行過采樣.

假設一個系統使用12 位的ADC,每秒輸出一個溫度值(1Hz),為了將測量分辨率增加到16 位,按下式計算過采樣頻率: fos=4^4*1(Hz)=256(Hz)。

1. AD轉換器的分類下面簡要介紹常用的幾種類型的基本原理及特點:積分型、逐次逼近型、并行比較型/串并行型、Σ-Δ調制型、電容陣列逐次比較型及壓頻變換型。 ?

1)

- 關鍵字:

ADC 基準源

- 系統設計人員正面臨越來越多的挑戰,他們需要在不降低系統組件(例如:高速 數據轉換器)性能的情況下讓其設計最大程度地節能。設計人員們可能會轉而采 用許多電池供電的應用(例如:某種手持終端、軟件無線設備或便攜式超聲波掃 描儀),也可能會縮小產品的外形尺寸,從而需要尋求減少發熱的諸多方法。 極大降低系統功耗的一種方法是對高速數據轉換器的電源進行優化。數據轉換器設計和工藝技術的一些最新進展,讓許多新型ADC可以直接由開關電源來驅 動,從而達到最大化功效的目的。 系統

- 關鍵字:

ADC LDO

Δ-∑adc介紹

您好,目前還沒有人創建詞條Δ-∑adc!

歡迎您創建該詞條,闡述對Δ-∑adc的理解,并與今后在此搜索Δ-∑adc的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473