Actel宣布Libero增添重要功能

——

Actel工具市場部高級經理Michael Mertz稱:“Libero 6.3 IDE結合業界最佳的第三方EDA工具和Actel的專有設計工具,延續了Actel以多功能工具套件提供無與倫比的價值的傳統。通過提升Libero來支持軟ARM7系列處理器的實施,我們可讓更多FPGA設計人員享用這種先進的微處理器技術。而且,透過將先前的人手作業自動化,并提供獨特的時序分析功能,FPGA設計人員更可迅速獲得最佳成果。”

經優化以支持CoreMP7

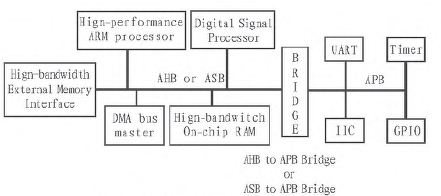

Libero 6.3提供先進的塊級方法,讓設計人員圍繞CoreMP7聚集IP,并以可預測的時序和驗證操作,將其映射在Actel的ProASIC3/E FPGA結構中。Libero 6.3緊密集成了來自Magma Design Automation、Mentor Graphics和Synplicity的業界領先的第三方工具,使到集成了CoreMP7的設計可實現無縫的綜合、驗證和物理綜合。Synplicity和Magma Design Automation的綜合和物理綜合工具中均有先進的黑盒子支持功能,能夠實現安全的設計流程,而Actel專有的工具則提供現代化的加密技術,保護具價值的ARM7 IP免遭非法存取。Actel的工具還提供所需的時序分析和布局功能,以簡化和加速采用CoreMP7的系統設計。

與以SRAM為基礎的器件不同,Actel難以侵入的Flash架構和功能強大的加密技術能保護ARM7和用戶IP免受反向工程或盜竊的問題影響,有助于保護公司的競爭優勢及開發投資。Libero 6.3為Actel器件提供獨特的端對端安全流程,容許首個以ARM處理器為基礎的技術能在可編程邏輯上作為軟IP內核實施。結果,設計人員能夠為各種以價值為基礎的消費電子、工業、汽車和高可靠性應用等,構建別具成本經濟的解決方案。

先進功能和新器件支持

Libero 6.3提供增強的時序和布局功能,能促進更佳的設計實施和提高設計人員效率。Actel領先業界的SmartTime時序分析環境現具有“強化的最小延遲” (Enhanced_Min_Delay, EMD) 功能,這個全面的工序首次將精確的保持時間分析功能引進于FPGA設計領域中。EMD能省去實現最小延遲的過度保守操作,以改進系統設計的時序收斂。這種顯著的性能提升以獨特方式為SmartTime用戶帶來優勢,通過更全面的方法來驗證內部和芯片至芯片級別的設置和保持時序。

Libero 6.3還采用先進的匹配算法,自動進行I/O電壓分配,緩解以處理器為基礎復雜設計的耗時工序,來優化I/O配置。這種新的I/O庫分配器在布局過程中,可以自動將VCCI電壓和VREF引腳分配至合適的未獲分配的I/O中。將這種先前以人手完成的過程自動化,可以簡化FPGA設計,尤其是包含多達80個不同種類I/O的復雜器件。

此外,Libero 6.3還提供所需的工具,針對采用Actel全新RTAX4000S器件的新一代高可靠性太空設計進行定標、布局和驗證操作。RTAX4000S具有400萬個系統門,是業界最高密度的耐輻射FPGA。

關于Libero集成設計環境

Actel的Libero 6.3 IDE集成了來自EDA伙伴最卓越先進的設計工具,包括Magma、Mentor Graphics、SynaptiCAD和Synplicity等各大EDA公司,以及由Actel定制開發的工具,集成至單一FPGA開發套裝中。Libero工具套裝支持混合模式設計輸入,讓設計人員可選擇在設計中將高級VHDL或Verilog HDL語言模塊與原理圖模塊混合起來。

評論