基于動態電源管理的移動終端設計(07-100)

供電部分是整個系統的基礎,這一部分作用非常重要,供電系統與耗電系統必須有緊密的聯系,可以互相通信,這樣才可大幅節省電能。如果系統各個元器件沒有質量問題,在焊接完成后就可以加電進行測試,所需要的工具和儀器儀表只要烙鐵、焊錫絲、數字萬用表就可以了。在焊接前,首先用萬用表測量最終的電壓輸出端和地有無短路現象,沒有才能進行焊接,目前許多制造PCB的廠家其做工和質量并不是很高,時常出現短路的現象。

本文引用地址:http://www.j9360.com/article/91987.htm動態電源管理

動態電源管理是調節移動終端中存在的一個或多個處理器內核的工作電壓和頻率,因為系統通常配備一塊高度集成的、基于 PowerPC、ARM 和 x86DSP 或智能基帶處理器。 系統功耗產生的原因與電阻上消耗的功率、有源器件的開關轉換階段以及集成電路內部和外部電容的充放電有關。另外,系統的性能指標、負載能力、被處理信號的工作頻率、電路的工作頻率、電源的管理水平、零部件的性能、散熱條件、接口的物理性能等都對系統功耗起著重要的作用。

目前絕大多數的處理器是用CMOS 工藝制造的。而CMOS電路的總功耗是動態功耗與靜態功耗之和,當電路工作或邏輯狀態轉換時會產生動態功耗,未發生轉換時晶體管漏電流會造成靜態功耗:

![]()

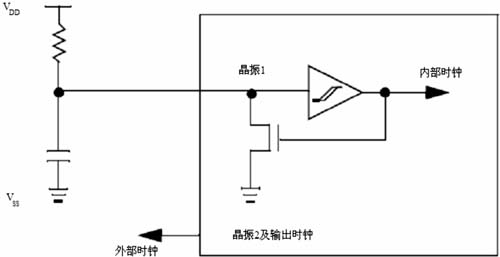

式中C為電容,為開關頻率,為電源電壓,為漏電流。為動態功耗,為靜態功耗。在電源管理設計實現中,重點是動態功耗。從式中可以看出:降低電壓對功耗的貢獻是2次方的;降低時鐘也可降低功耗,但它同時也降低性能,延長同一任務的執行時間。所以,選擇滿足性能所需的最低時鐘頻率,在時鐘頻率和各種系統部件運行電壓要求范圍內,設定最低的電源電壓,將會大量減少系統功耗。基于這種思想的電源管理方法如圖2所示,它能動態的改變CPU時鐘,降低處理器的時鐘頻率。

圖2 動態電源管理方法

評論