高速信號、時鐘及數據捕捉(05-100)

——

本文引用地址:http://www.j9360.com/article/91444.htm

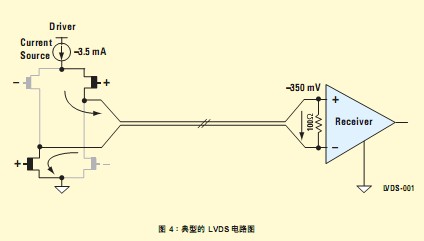

圖4 典型的 LVDS 電路圖

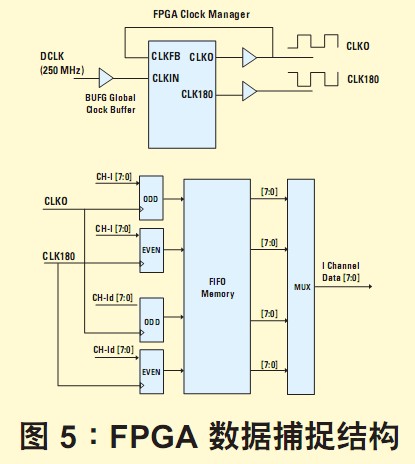

圖5 FPGA 數據捕捉結構

為了簡化這個定時上的規定,FPGA 都設有數字時鐘管理電路。基本上,這些時鐘管理電路都屬于鎖相環路 (PPL) 或延遲鎖定環路 (DLL),其優點是可以容許由內部產生時鐘信號,并確保所有時鐘信號的相位都按照輸入時鐘鎖定,其分接頭的相位延遲分別為 0、90、180 及 270。這種時鐘管理技術的優點是可以提供準確的 180 位移時鐘,使 DDR 定時電路可以順暢地執行其正常功能,以便 FPGA 存儲器可以捕捉與下降邊緣同步的輸入信號,然后利用數據閂鎖將輸入數據妥善保存。鎖定后的輸入數據可以再傳送往先進先出存儲器或數據塊 RAM,以便系統微控制器可以輕易以遠比先前慢的速度檢索有關數據,然后才作進一步的處理。

結語

系統設計工程師若要設計一個完善的超高速數據轉換系統,需要面對很多挑戰。這類轉換系統是真真正正的混合信號系統,我們必須小心考量所有子電路的優缺點,才可確保模/數轉換器能夠充分發揮其強勁性能。工程師只要采用現成的元件,便能以極低的成本組建符合低抖動要求的定時系統。此外,目前市場上提供的 FPGA 芯片都可為必須全面符合 LVDS 規定而又需要加設時鐘管理電路的系統提供支持。■

評論