基于Verilog-HDL的軸承振動噪聲電壓峰值檢測

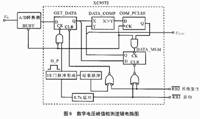

僅有圖5的邏輯功能框圖還不能方便地用Verilog-HDL來描述。為此將其進一步細化為圖6所示的形式。圖6中虛線框內的功能由XC9572(Xilinx公司的產品)實現。圖6中,Vin為模擬電壓的輸入,VDOUT為數字峰值電壓的輸出,VDOUT、RB1、RB21均與接口電路相接,RB1、RB2受微機的控制。

本文引用地址:http://www.j9360.com/article/83375.htm

2.2 時序圖

圖7為圖6所示邏輯電路的時序圖。按照軸承檢測的工藝,當系統復位RB2、啟動脈沖RB1到來后,經0.7s的延時,便產生1個寬度為1s的門脈沖G_P。在此期間,A/D轉換器連續轉換的數據送入數據緩沖器GET_DATA,之后進行數字信號的峰值檢測和保持。A/D轉換器在此采用MAX120。該轉換器的分辨率為12bit,轉換時間為1.6μs。2.3 邏輯仿真。

在硬件電路實現之前,用Verilog-HDL對圖6所示的邏輯電路進行了仿真,圖8即為仿真結果。從仿真結果中可以看出,系統復位后,D_OUT(VDOUT)輸出為0,在1s門脈沖G_P有效期間,GET_DATA接收時鐘GET_DATA_CLK。此間來自A/D轉換器的數字電壓(分別為FROM_ADC=10、15、18、17、4、6、2)相繼輸入至GET_DATA。由于這期間的最大值為FROM_ADC=18,故有D_OUT=18。在門脈沖G_P無效期間,即使有數據FROM_ADC=11輸入,仍有D_OUT=0。

2.4 Verilog-HDL主模塊

限于篇幅,這里只將本系統所涉及到的Verilog-HDL的主模塊部分列出:

Module PK_SEL(BUSY,RB1,RB2,FROM_ADC,D_OUT,P_OUT);

input BUSY,RB1,RB2;

output P_OUT;

input [11:0]FROM_ADC;

output [11:0]D_OUT;

wire [11:0]TO_COM;

wire GET_DATA_CLK;

//產生秒脈沖

CNT100 F_4kHz (RB1,BUSY,F_4k); //分頻

CNT100 F_37Hz (RB1,F_4k,F_37); //分頻

DELAY_P1 START_DLY (RB2,RB1,F_7,DLY_05S); //延時0.7s

DELAY_P2 GENE_SPB (RB2,DLY_05S,F_7,SPB); //延時1s

GETE_GENE GENE_GP (G_P,DLY_05S&RB2,SPB); //1s的門脈沖

Assign P_OUT=G_P;

//ADC數據最大值的比較和檢測

assign GET_DATA_CLK=~BUSY & G_P;

DFF12 GET_DATA(GET_DATA_CLK,FROM_ADC,TO_COM, ~SPB & RB2); //獲取ADC數據

COMP_D DATA_COMP(TO_COM,D_OUT,D_S); //數據比較

DFF12 DATA_MEM(BUSY & D_S,TO_COM,D_OUT,RB1 & RB2); //數據存儲

endmodule

結束語

與模擬式的峰值電壓檢測方式相比,數字式的檢測方式有著結構簡單、系統開發周期短等優點,而采用Verilog-HDL可以方便地實現欲有的功能。筆者設計開發的該系統用在了大連科匯軸承儀器有限公司生產的S0910-3型軸承振動測量儀中,并于2001年6月在上海的國際軸承及裝備博覽會上引起了同行的關注。

評論