MCS-51單片機串行口IP核的實現

1 引言

隨著集成電路的深亞微米制造技術和eda技術的迅猛發展,芯片的密度和復雜度不斷提高,復用以前的設計模塊用于asic芯片和在一塊芯片上實現嵌入式系統的功能形成所謂的片上可編程系統( system on programmable chip,sopc) 已成為一種發展的新趨勢。ip core(知識產權核) 設計的重用性以及sopc 技術的出現,以其設計的靈活性大大縮短了產品的設計周期,減少了設計成本,降低了設計風險,加快了產品的上市速度。本文中介紹的串行口控制器是一種功能和通信協議與MCS-51系列單片機的串行口相兼容,性能有大幅提高的數據通信部件,其往往于低速低成本的微機與下位機的通訊中,并允許在串行鏈路上進行全雙工的通信。通過IP核重用技術,可廣泛應用在各種soc、嵌入式微處理芯片的設計以及工業應用中。

2 系統簡介

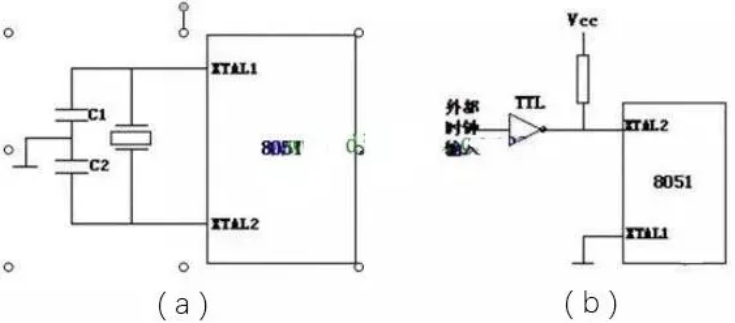

本課題采用altera公司的max+plusⅱ10.0設計平臺,以超高速集成電路硬件描述語言vhdl為系統邏輯描述的唯一表達方式,采用自頂向下的設計原則,對mcs-51單片機的串行接口進行反相設計。同時選用altera公司的acex系列器件來實現最終的ip核。由于篇幅的關系,筆者不打算對開發平臺、開發工具以及最終實現硬件電路的fpga芯片進行介紹,而是著重介紹整體的設計思想。根據對mcs-51單片機的串行接口塊功能的剖析[1]和模塊化的設計思想,在設計時進行模塊劃分,可劃分為4個子模塊,它們分別是:(1)串口時鐘發生器模塊;(2)數據檢測器模塊;(3)發送器模塊;(4)接收器模塊。由于同步電路較容易使用寄存器的異步復位/置位端,可以使整個電路有一個確定的初始狀態;使用同步電路易于消除電路的毛刺,使設計更可靠;同步電路可以很好地利用先進的設計工具,如靜態時序分析工具等,為設計者提供最大便利條件,便于電路錯誤分析,加快設計進度。所以我們采用嚴格的同步設計電路來設計串行口ip核,即本設計中只有一個clk上升沿,從而保證了每一個觸發器同步動作,消除了時鐘不同步帶來的誤動作。

3 系統現實

設計一個軟核,首先要確定本核與外部的信息交換通路,即本模塊與外部電路的接口,友好的接口模型可以大大提高ip核的使用范圍。圖1是串行口ip核的接口模型圖,圖中左邊的引腳是輸入引腳,右邊是輸出引腳,圖中引腳的寬度均有標明(未寫出寬度表明寬度為“1”)。由于本設計不支持i/o口的復用,所以為串行口工作于模式0下增加了rxd_o和rxdwr兩個輸出引腳,前者用于輸出,后者為輸出有效控制位(rxdwr為高電平時,指示輸出)。串行口控制寄存器scon在設計中也被分成兩部分,一部分接收來自控制器的輸入(一共6位, sm0、sm1、sm2、ren、tb8和ri),一部分作為輸出送往控制器(一共3位,rb8以及分別指示發送和接收完畢的兩位,控制器會根據這兩位來對中斷標志置位)。至于發送中斷標志位ti,由于其不會影響串行口的工作過程所以在此并未列出,它將在控制器中得到體現。

圖1 串行口輸入輸出引腳圖

串行口有四種工作方式,方式0的波特率固定的(為1/12倍的輸入時鐘頻率);方式1和方式3的波特率是定時器/計數器1的溢出率的1/16或1/32倍;而方式2的波特率則是輸入時鐘頻率的1/32或1/64倍。由此可見,首先必須要解決的問題就是設計分頻器。由于在方式0下,串行口是作半雙工的同步移位寄存器使用,其發送和接收的波特率是一樣的,因此對于方式0,串行口內部的分頻信號只需要一路即可。但是對于其他方式,串行口均是工作在全雙工的狀態下,因此,每種方式下均需要兩路分頻信號,一個用于發送,一個用于接收。

對于方式0和方式2,其分頻的對象是輸入時鐘,實現這種分頻器的主要vhdl代碼的如下:(信號s_count_enable的頻率為輸入時鐘頻率的1/12,其高電平維持時間與一個輸入時鐘的周期相等。)

s_count_enable<=`1`when s_pre_count=conv_unsigned(11,4) else `0`;

p_divide_clk: process (clk, reset)

begin

if reset = `1` then

s_pre_count <= conv_unsigned(0,4);

else

{{分頁}}

if clk`event and clk=`1` then

if s_pre_count = conv_unsigned(11,4) then

s_pre_count <= conv_unsigned(0,4);

else

s_pre_count <= s_pre_count + conv_unsigned(1,1);

end if;

end if;

end if;

end process p_divide_clk;

對于方式1和方式3,其分頻的對象都是定時器/計數器1的溢出率,且分頻的系數是一樣的。由于串行口只有一個,它不可能調試工作在方式1和3,因此方式1和方式3可以共用分頻信號。要對定時器/計數器1的溢出率進行分頻,首先必須測出其頻率,為此需要一個上升沿的檢測器來監測外部輸入的定時器/計數器1的溢出信號(圖1中的tf_i引腳),這樣的檢測器可以雙穩態觸發器來實現,限于篇幅,雙穩態觸發器的vhdl實現請參考文獻[2],這里就不加詳述。檢測器在監測到tf_i引腳的上升沿時就使其輸出信號保持一個時鐘周期的高電平,再另外設計計數器對此高電平進行計數,以達到對其分頻的效果。

除了作為同步移位寄存器的方式0外,其他作uart(通用異步接收和發送器)用的三種方式在接收外部輸入的時候均需要對外部的輸入信號采樣監測以確定信號的值。因此一個位檢測器是必需的。同時,串行口工作在方式1、方式2和方式3時,每一個接收的數據幀都有一個起始位,這個起始位被固定為0,也就是說在輸入端rxd_i監測到1到0的跳變就會啟動接收過程(注:負跳變檢測器對外部輸入引腳的采樣頻率為波特率的16倍)。負跳變檢測器和上述上升沿檢測器的設計思路是一樣的。位檢測器的設計原理是把一個接收位的時間分為16等分(以內部計數器的16個狀態來表示),在計數器的7、8、9狀態時,位檢測器對外部輸入端的值進行采樣。采用3取2的表決方法來抑制噪聲。如果位檢測器檢測到接收的第一位不是0,那么就說明它不是一幀數據的起始位,應該擯棄,接收電路復位。

至于接收器和發送器,這里采用有限狀態機的方式來實現。由于要工作在全雙工模式下,所以接收和發送要采用兩個有限狀態機。有限狀態機的每一個狀態用來發送/接收移位數據。發送和接收的具體實現方式是移位。移位的時鐘來自上面所述的分頻器的,也就是根據各自的波特率進行。雖然此部分很繁瑣,但是實現并不困難,請讀者參閱文獻[3]、[4]和[5]。

4 模塊功能仿真

圖2是串行口工作在方式0下發送數據的仿真圖。輸入信號trans_i是發送的啟動信號(高電平有效)。它的出現使內部用于發送的狀態機啟動,同時使內部計數器復位,以便使每位的發送過程與計數器同步。計數器滿刻度偏轉一次,狀態機的狀態就會增加1。如圖所示,在狀態0向狀態1轉換時,將要發送的8位數據的最低為輸出到rxd_o,這一數據的電平一直維持到狀態1向狀態2轉換,這時開始輸出第二位數據。依此類推,在狀態8的末尾,8位數據完全輸出完畢后,指示是否有數據輸出的信號rxdwr_o變為低電平,表示數據已經發送完畢。同時,發送完成的指示信號(scon_o[0…2]中的相應位)也會置位。

{{分頁}}

圖2 工作于方式0的串行口發送數據的仿真圖

圖3是工作于方式0的串行口接收數據的仿真圖。接收狀態機的啟動依靠的是輸入信號 ren、ri。當ren=1且ri=0時,就會啟動一次接收過程。如圖中所示,接收過程始于狀態0的末尾scon_i的ren=1的時候(圖中左邊的豎線處),而在下一個狀態(狀態1)的末尾就會將外部輸入引腳的值移入內部的移位寄存器,依此類推,直到狀態8的末尾將第8位數據移入,同時使接收緩沖寄存器和sbuf_o的值都為剛才移位所得到數值,以送往控制器處理。同時,接收完成的指示信號(scon_o[0…2]中的相應位)也會置位。

圖3 工作于方式0的串行口接收數據的仿真圖

圖4是工作于方式1的串行口的接收和發送數據同時進行的仿真圖。方式1中發送和接收數據的時鐘源自tf_i。其發送的啟動信號仍然是trans_i;接收的啟動信號是檢測到外部輸入信號rxd_i有負跳沿出現。如圖中所示,在接收狀態機的狀態0的末尾,負跳沿被檢測到,狀態機馬上啟動,轉入下一個狀態1。在狀態1中,三次掃描檢測rxd_i引腳的值,如果有兩次或者三次值是“0”,則說明收到的起始位的值是“0”,狀態機轉入下一狀態準備接收數據位,依此類推直到狀態9的末尾將8位數據位最后一位收到并移如移位寄存器。再在下一個狀態(狀態10)接受停止位,如果停止位有效(停止位送至rb8,圖中的scon_o(2)),則將接收到的數據送到接受緩沖區,并輸出。至于發送,首先要發送的是起始位“0”,最后還要發送一位停止位“1”,上圖中很清楚的表示了這一過程。

圖4 工作于方式1的串行口發送、接收數據的仿真圖

圖5是工作于方式2的串行口的接收和發送數據同時進行的仿真圖。方式2和方式1的接收和發送的工程是一樣的。不同的在接收時,它用來送入rb8的值不是停止位而是可編程控制位,同時也是根據對這一位的判斷來決定接收是否有 效。(圖中接收的可編程控制位是“1”)在發送時,它在停止位之前還發送一位可編程控制位tb8(圖中scon_i的最低位)。

圖5 工作于方式2的串行口發送、接收數據的仿真圖

{{分頁}}

至于方式3下串口的工作情況,除波特率不同外,其他與方式2完全一樣,圖6是工作于方式3的串行口的接收和發送數據同時進行的仿真圖。

圖6 工作于方式3的串行口發送、接收數據的仿真圖

5 結束語

本文設計的兼容MCS-51單片機的串行口IP核采用完全同步的設計,系統在統一的時鐘下工作。時鐘周期只與所選用的fpga/cpld芯片的延時有關,而與設計無關,因此,串行口的波特率可根據時鐘周期任意調整。另外,此串行口ip 核已經結合其它ip核做成了一個soc系統,并成功地通過了fpga的測試。

評論