ARM9微控制器LPC3180的軟硬件平臺設計

摘要 介紹以Philips LPC3180微控制器為核心的嵌入式軟硬件平臺設計;對系統設計的硬件部分和軟件部分進行詳細的分析,并針對LPC3180芯片特性著重討論了其軟件系統構建以及系統啟動流程。實驗結果表明,LPC3180嵌入式系統平臺結合片內硬件浮點運算單元,具有高性能的浮點運算處理能力,可滿足復雜的嵌入式應用場合的要求。

關鍵詞 LPC3180 ARM9 軟硬件平臺

嵌入式應用系統設計包括硬件平臺和軟件平臺兩部分。前者是以嵌入式微控制器/微處理器為核心的硬件系統;后者則是圍繞嵌入式操作系統構建的軟件系統。兩者在設計上是密不可分的,并且需要在設計之間進行權衡優化,根據實際應用進行外擴和裁剪。

基于ARM926EJS內核的LPC3180內部集成了豐富的外設資源,為嵌入式系統構建提供了很大的設計空間。本文結合筆者開發LPC3180嵌入式平臺的實際經驗,將具體介紹該系統的實現、結構組成和實驗結果。

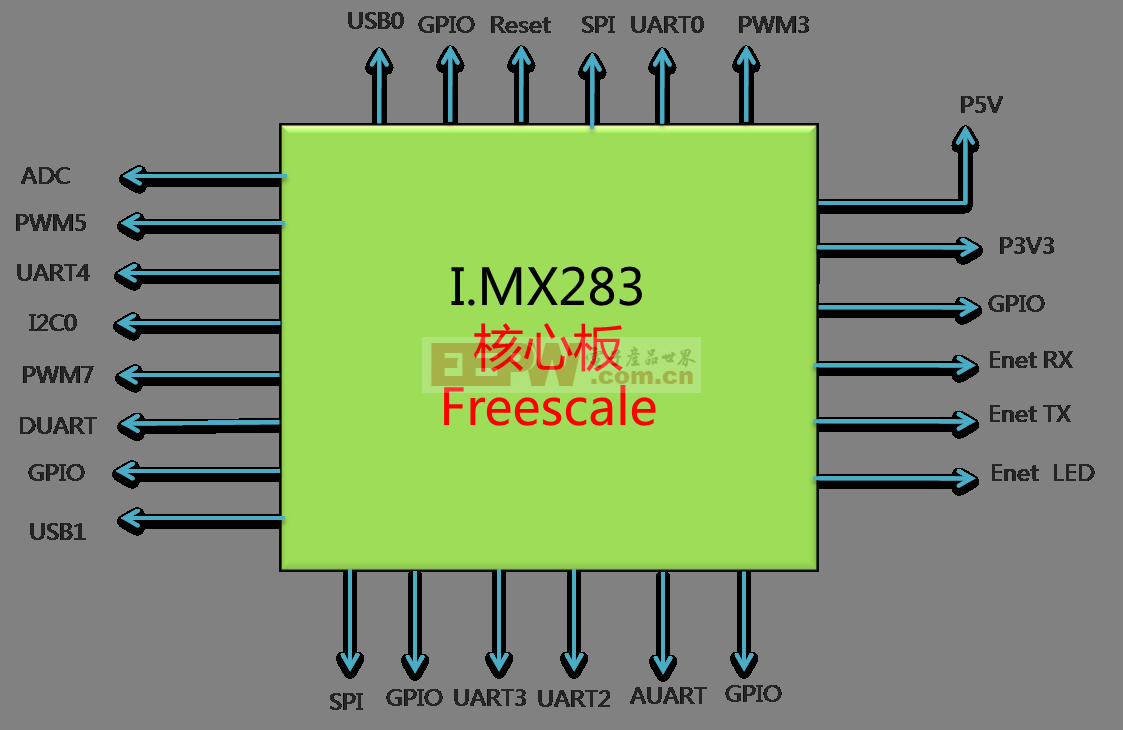

1 LPC3180芯片特性介紹

LPC3180是Philips公司新推出的一款ARM9微控制器。它采用90nm工藝技術,片內集成ARM9EJS處理器內核,具有高計算性能、低功耗的特性,這使得在很多對功耗敏感的嵌入式應用場合中仍能使用高性能的ARM9微控制器。LPC3180內核正常工作電壓為1.2V,在低功耗模式下可降至0.9 V;同時,LPC3180作為一款新型的32位微控制器,其新特性還包括:

◆ 片內集成向量浮點(VFP)協處理器。LPC3180的浮點運算單元有3條獨立的流水線,支持并行單精度或雙精度浮點加/減、乘/除以及乘累積運算,完全兼容IEEE754標準,適用于高速浮點運算場合。

◆ 片內集成USB OTG控制模塊,同時支持與便攜USB主設備或USB外設相連,可用于與PDA、讀卡器和打印機等設備直接相連,而無需PC機介入。

◆ LPC3180采用多層的AHB總線系統,為各個主模塊提供獨立的總線,包括CPU的指令總線和數據總線、2套DMA控制器數據總線以及1套USB控制器數據總線。

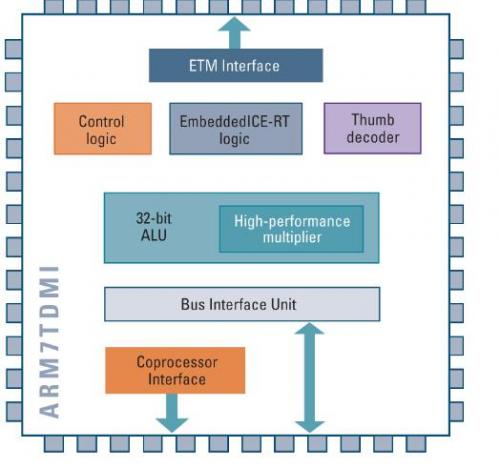

LPC3180的內部架構如圖1所示。

圖1 LPC3180內部架構 {{分頁}}

LPC3180的其他特性包括: 內部集成MLC/SLCNAND控制器、SDR/DDR SDRAM控制器、SD卡接口,UART、SPI、I2C外圍通信模塊,以及高速/毫秒定時器、RTC、看門狗定時器、10位ADC等其他功能模塊。

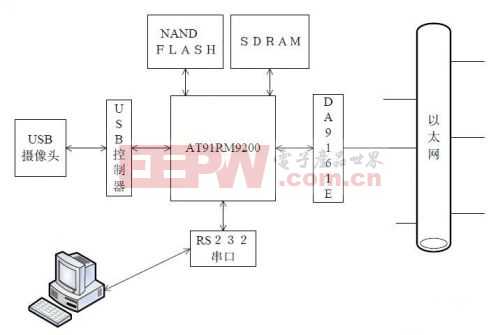

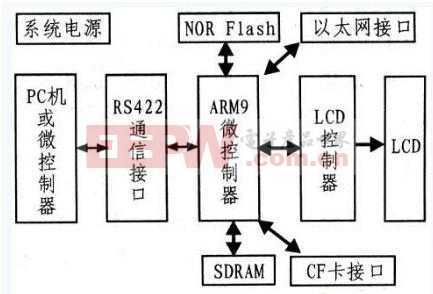

2 硬件平臺設計

以LPC3180為核心的硬件平臺設計框架如圖2所示。

圖2 LPC3180硬件平臺設計框圖

(1) 存儲器系統

NAND Flash存儲器。通過LPC3180內部集成的MLC/SLC NAND控制器直接外接多級或單級NAND Flash器件。本系統選用ST NAND256R3A,其32 MB存儲空間可滿足存放系統引導程序、嵌入式操作系統內核和文件系統的大小要求。

SDRAM存儲器。系統選用2片16位MICRON SDRAM,并聯構建32位SDRAM存儲器系統。32 MB SDRAM空間,可滿足嵌入式操作系統以及上層應用程序的運行要求。

SD卡插槽。系統通過LPC3180內部集成的SD卡接口,提供SD卡插槽,可用于SD存儲卡外擴,作為外部存儲空間。

(2) 外圍通信接口

UART接口。LPC3180內部集成了標準UART模塊和高速UART模塊,符合550工業標準。系統外擴了UART1/7、UART2和UART5,用于實現基本的串行通信功能;同時,UART5可用于系統啟動時的外部程序下載。

USB接口。LPC3180內部集成了USB host、USB device以及USB OTG控制器,通過外部USB收發模塊Philips ISP1301外擴USB host接口A、USB device接口B以及USB OTG接口AB。 {{分頁}}

(3) 其他外圍模塊

系統通過I2C接口外擴了一個簡易的字符型LCD顯示模塊,用于應用程序運行結果顯示;同時,為了簡化硬件系統設計,系統的以太網模塊通過USB host接口A以軟件方式實現外擴。

3 系統關鍵模塊設計

3.1 NAND Flash存儲器模塊

LPC3180內部集成了MLC/SLC NAND控制器,通過外部引腳可直接外接多級或單級NAND Flash器件,如圖3所示。需要注意的是MLC和SLC NAND控制器通過引腳復用,使用相同的接口與NAND Flash相連,且同一時刻只允許開啟其中一個控制器,因此在系統上電后必須通過配置FLASH_CTRL寄存器選擇要使用的NAND控制器。在閑置狀態時,也可通過寫寄存器關閉NAND控制器,以降低功耗。NAND Flash存儲器模塊是整個系統主要的靜態數據存儲空間,用于存儲系統啟動過程中的加載程序,因此在LPC3180系統設計中是必不可少的。

圖3 NAND Flash接口連接圖

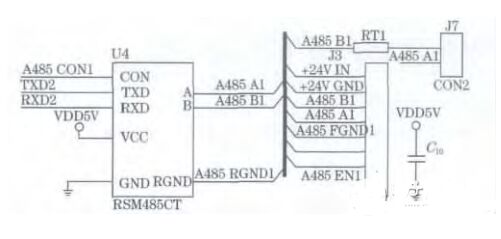

3.2 USB接口模塊

LPC3180內部集成USB控制模塊,但不包括USB物理層,系統通過外接USB收發模塊ISP1301實現USB的物理層接口。圖4是USB接口連接圖。LPC3180內部通過AHB從設備總線配置USB控制器,可工作在全速(12 Mb/s)和低速(1.5 Mb/s)兩種模式下。

圖4 USB接口連接圖 {{分頁}}

4 軟件系統設計

軟件系統組成包括系統引導程序Bootloader,嵌入式操作系統以及上層應用程序。其中Bootloader是運行于操作系統之前的引導程序,主要任務是完成系統啟動之前必要的硬件初始化和操作系統加載;操作系統是整個嵌入式平臺的核心程序,主要功能是高效地管理和分配底層硬件資源,并為上層應用程序提供與硬件細節無關的系統調用接口。

軟件系統設計必須與硬件平臺緊密結合。LPC3180采用NAND Flash作為整個系統的程序存儲區域,在系統啟動時通過片上ROM的bootstrap程序,從NAND Flash加載并執行外部引導程序來實現整個系統的啟動步驟。因此,整個軟件系統采取了圖5所示的設計結構。

圖5 軟件系統結構框圖

(1) 系統引導程序Bootloader

由于啟動過程首先從片內的bootstrap程序開始,因此系統采取二級Bootloader設計,包括第一級Sibl和第二級Uboot。

其中Sibl是bootstrap加載并執行的第一個引導程序,在程序大小上受到bootstrap加載的限制,因此設計上盡量做到了小型化和功能專一。它除了完成最基本的硬件初始化以外,主要功能是實現其他程序(包括Uboot)從NAND Flash的加載,完成下一級Bootloader運行之前的內存地址空間分布。

第二級Bootloader采用功能強大的sourceforge開源軟件Uboot。Uboot的主要功能是完成嵌入式操作系統啟動前的底層硬件初始化,并為Linux內核提供啟動參數,最終引導操作系統Linux內核啟動。另外,為了實現程序鏡像文件編程寫入NAND Flash,Uboot嵌入了一個NAND子系統,通過Uboot的用戶命令行實現對NAND Flash的讀/寫操作,可將程序鏡像寫入NAND Flash指定的地址空間。

(2) 嵌入式操作系統

LPC3180內部集成了ARM926EJS處理器內核,帶存儲器管理單元MMU,支持多數主流嵌入式操作系統。系統通過編寫板級支持代碼,移植了Linux2.6.10作為平臺操作系統,利用穩定的Linux2.6內核實現任務調度、進程管理、內存管理等功能,同時,針對Linux的可配置性,對內核進行裁剪和硬件驅動代碼添加,系統實現了一個小型但功能強大的內核程序,適應了嵌入式系統存儲資源相對緊缺的狀況。

5 系統啟動流程分析

由上面的軟件結構組成分析可知,整個系統啟動流程分為3個步驟:

① 系統上電后,首先從片上ROM固化的bootstrap程序執行。bootstrap用于完成外部引導程序下載并跳入執行。bootstrap運行過程首先讀輸入引腳GPIO_01。如果GPIO_01置為高,則從NAND Flash下載程序引導系統啟動;如果置為低,則依次檢測USB接口和UART5接口,通過外部連接下載引導程序。系統通過設置GPIO_IO跳線來控制bootstrap啟動過程,本例將GPIO_01置為高,從NAND Flash下載程序。

② 系統啟動的第二階段是運行bootstrap下載的引導程序Sibl。Sibl完成系統必要的初始化后,從NAND Flash加載鏡像程序到指定的SDRAM空間。鏡像程序在起始位置添加了64字節的頭信息,用于Sibl識別和加載,頭信息數據結構如下:

struct image_header {

uint32_tih_magic;/*鏡像頭信息同步字,Sibl通過該字識別程序*/

uint32_tih_hcrc;/*鏡像頭信息CRC校驗碼*/

uint32_tih_time;/*存儲鏡像創建時間*/

uint32_tih_size;/*鏡像數據大小*/

uint32_tih_load;/*鏡像加載地址*/

uint32_tih_ep;/*鏡像入口地址*/

uint32_tih_dcrc;/*鏡像數據CRC校驗碼*/

uint8_tih_os;/*操作系統信息*/

uint8_tih_arch;/*CPU體系結構類型*/

uint8_tih_type;/*鏡像類型*/

uint8_tih_comp;/*壓縮類型*/

uint8_tih_name[32];/*鏡像名稱*/

}{{分頁}}

Sibl從NAND Flash起始地址開始搜索。如果讀到鏡像同步字ih_magic,則識別鏡像程序,并根據偏移地址讀取程序大小ih_size和加載地址ih_load,將程序加載到指定的SDRAM空間;加載完成后根據CRC校驗碼ih_dcrc對SDRAM數據進行CRC檢測;最后根據鏡像類型ih_type判斷鏡像是否可執行,若可執行,則跳入鏡像入口地址ih_ep,否則Sibl繼續搜索NAND Flash鏡像程序。

鏡像程序使用U-boot提供的工具mkimage添加頭信息,命令格式如下:

mkimage-A arch-O os-T type-C comp-a addr-e ep-n name-d data_file image

圖6 系統啟動過程內存空間分布圖

③ 完成Sibl加載后,內存空間分布如圖6所示,系統進入啟動流程的第三階段U-boot。U-boot完成Linux內核鏡像的解壓縮和操作系統啟動前的初始化,最終跳入內核入口地址,完成對Linux的引導。

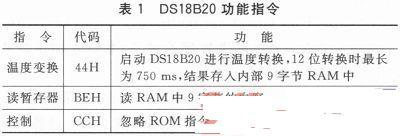

6 系統性能分析

系統構建提供了一個完整的LPC3180嵌入式軟硬件平臺,下面對LPC3180浮點運算能力進行測試和分析。測試方法是使用一個浮點運算密集的算法,用ADS編譯器分別編譯使能硬件VFP和軟浮點運算兩個版本的測試程序,并在不同的CPU時鐘頻率下比較運行時間,結果如表1所列。

分析實驗數據,可以得出結論:VFP協處理器在相同時鐘頻率下,提高了5倍左右的浮點運算性能。因此,LPC3180平臺結合VFP協處理器,能夠實現復雜的浮點運算密集算法。在微控制器中集成硬件浮點運算單元,這使得微控制器的數據處理能力大大提高,能夠勝任多數的數字信號處理應用。

表1 浮點運算結果

結語

本文介紹了以LPC3180微控制器為核心的嵌入式軟硬件平臺的設計與實現,并測試、驗證了LPC3180的浮點運算性能。該平臺對于LPC3180的應用開發具有借鑒意義。目前LPC3180在醫療器械、工業控制、POS機、數字信號處理等領域有著廣泛的應用。

參考文獻

[1] LPC3180 User Manual. http://standardics.philips.com.

[2] ISP1301 User Manual. http://semiconductors.philips.com.

評論