使用Quartus II提高可編程邏輯設計效能的T.I.P.S

Altera

今天每一個工程人員都把精力放在效能上面,即用最少的資源做最多的事情。Altera的PLD開發軟件平臺工具Quartus II 能幫助工程人員提高效能,它是如何實現的呢?概括起來說就是 Quartus II的T.I.P.S.

• T代表Timequest, ——新一代ASIC功能時序分析儀,支持業界標準Synopsys設計約束(SDC)時序分析方法。

• I代表增量式編譯(Incremental Compilation)支持自下而上的設計流程,可以分別建立和優化設計模塊。系統體系結構可以逐步集成經過優化的設計模塊,在整個集成過程中,保持設計模塊的性能不變。

• P 代表PowerPlay功耗分析和優化技術:它能夠對功耗進行自動優化,從設計概念形成到實施階段,幫助您提高功耗管理的效率。

• S 代表SOPC Builder,它避免了繁雜而又容易出錯的系統集成任務,幫助您迅速建立系統。

T: TimeQuest

TimeQuest時序分析儀應用于標準FPGA時序驗證

新的、使用方便的TimeQuest時序分析器提供完整的GUI環境,建立約束和時序報告,并提供ASIC功能特性,自然地支持Synopsys設計約束(SDC)格式,以及全腳本功能。TimeQuest時序分析器是 65nm 器件和未來工藝技術的默認時序分析器。 Altera 的 Quartus® II 軟件針對 65nm 和以前的設計繼續提供標準時序分析器。

誰應該使用TimeQuest時序分析器

Altera建議在180nm、90nm和65nm工藝節點上所有新的Altera® 設計都使用 TimeQuest 時序分析器。此外,還建議所有移植到65nm器件上的設計都使用TimeQuest時序分析器。

注意: 移植到65nm器件上包括存儲器接口 (DDR、DDR II等)的設計應使用TimeQuest時序分析器,而不要使用標準時序分析器。

和標準時序分析器相比,為什么要使用 TimeQuest 時序分析器

從基本的時序分析要求到高級時序分析要求,與標準時序分析器相比,TimeQuest時序分析器都有明顯的優勢。

• 基本時序分析要求—— TimeQuest 時序分析器提供使用方便的GUI,建立約束,查看時序報告。使用 TimeQuest 時序分析器,它提供和標準時序分析器相同的流程 ( 包括默認的時鐘約束和 fMAX 報告 ) ,您不必再學習SDC或者其他的約束格式。而且,與標準時序分析器相比, TimeQuest 時序分析器提供更多的約束對話框,加速建立約束。

• 中間時序分析要求—— TimeQuest 時序分析器能夠自然地支持 SDC 格式。 TimeQuest 時序分析器簡化了 SDC 的學習過程,提供按需的交互式報告功能。 與 標準時序分析器相比, TimeQuest 時序分析器能夠建立更精確的時序行為模型 ( 例如,上升 / 下降時序模型 ) 。 Hardcopy II 和 65nm 器件系列的性能可以提高 3-5 %。

• 高級時序要求—— TimeQuest 時序分析器提供全腳本功能,建立約束,生成報告,管理時序分析流程。 TimeQuest 時序分析器支持高級 (though- 支持 ) 報告,并且能夠建立定制報告。 TimeQuest 時序分析器簡化了對源同步接口 (DDR 、 DDR2) 的約束。而且, TimeQuest 對 SDC 的自然支持還能夠輕松實現 ASIC 原型開發,或者移植為 Hardcopy 結構化 ASIC 。

{{分頁}}

I: Incremental Compilation (增量式編譯)

Quartus II 編譯增強特性

高密度 FPGA 設計的性能和效能達到最佳

Quartus® II 軟件首次實現了 FPGA 業界的漸進式編譯功能,支持自上而下和自下而上基于團隊的設計,縮短了設計迭代的編譯時間,同時保持性能不變,使 Quartus II 軟件成為高密度 FPGA 設計中效率最高的軟件。使用 Quartus II 軟件來進行高密度 FPGA 設計,您可以迅速完成設計。

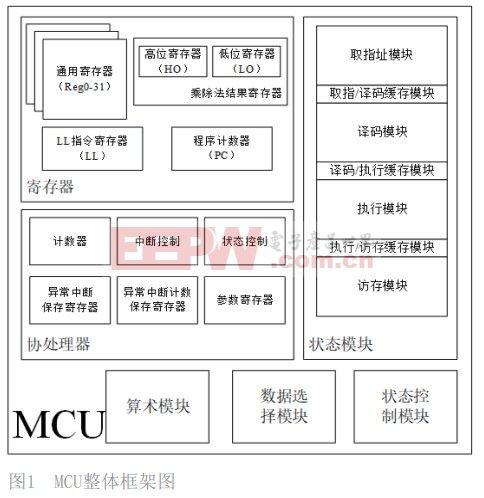

在系統集成過程中,保持設計模塊的性能不變

Quartus II 漸進式設計在功能上的改進包括了基于團隊的工程管理流程,大大提高了團隊設計的效率。系統規劃人員可以首先采用自上而下的方法定義一個工程。在新的工程管理器界面中 ( 參見圖 1) ,您可以生成所有的自下而上的設計分區工程,讓每個工程師獨立地進行開發和優化,然后將結果集成到整個設計中。在系統集成階段,系統規劃人員還可以對準備好的優化設計模塊逐步進行集成,同時保持設計模塊的性能不變。

圖 1. 工程管理器 GUI

每天進行更多的迭代,實現最大效能

通過縮短編譯時間 ( 參見圖 2) ,您可以由原來的每天只能迭代一到兩次提高到現在的四到十次,極大的提高了設計效能。

圖 2. 縮短高密度 FPGA 設計的編譯時間,進行更多的迭代

更快地達到時序逼進

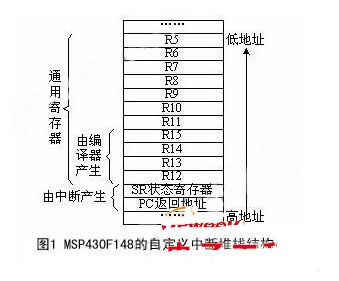

漸進式編譯功能使設計人員能夠為綜合和適配 / 邏輯布局確定物理和邏輯分區,如圖 3 所示。

圖 3. 漸進式編譯的設計分區

Quartus II 軟件在處理設計時,保留您指定的分區,使您能夠優化特定分區而保持其他分區不變。高級優化技術會導致編譯時間增加,而漸進式編譯功能則使降低了這種影響,提高時序逼近性能,在特定設計分區上使用物理綜合等高級優化技術,保持其他分區不變。

例如,如果頂部分區和 F 分區 ( 參見圖 3) 已經達到性能要求,那么您可以只修改 B 分區或者打開物理綜合功能,重新編譯設計來進一步優化設計的總體性能。

使用方便

如圖 4 所示,可以方便的在 Quartus II 軟件工程導航器層次視圖中分配分區。

圖 4. 在用戶界面中確定設計分區

完成設計分區后,設計人員通過為每個分區設置一個網表類型屬性,實現對設計處理過程的高級控制。表 1 是一些有效的設置。

{{分頁}}

P: PowerPlay功率分析和優化

Quartus II PowerPlay功率分析和優化技術

引入Quartus® II 的PowerPlay功率分析和優化技術后,Altera在軟件技術上領先的傳統,得到了進一步的鞏固。PowerPlay技術可以使您對動態和靜態功耗進行精確的分析和優化。在2005年即將發布的Quartus II新版本中,PowerPlay功率分析工具能夠滿足速度和面積的要求,提供按鍵式靜態和動態功耗優化。

從設計概念產生到實施過程中的功率分析

Quartus II PowerPlay功率分析工具使您能夠在早期設計概念產生到設計實施階段過程中對功耗進行估算,如圖2所示。

圖2. PowerPlay功率分析

PowerPlay早期功率估算器

設計人員可以在設計概念產生階段利用PowerPlay早期功率估算器表單對靜態和動態功耗進行估算。利用新的Quartus II PowerPlay功率分析器功能,能夠在設計實施階段對功率進行精確估算。

PowerPlay功率分析器

Quartus II軟件現在具有PowerPlay功率分析器功能,通過早期功率估算器表單,該功能提高了功耗估算的精度。該表單:

• 考慮器件資源使用和布局布線結果

• 考慮功能和時序仿真輸入/輸出激勵

• 當仿真矢量輸入無效時,對預期的設計節點工作速率進行統計分析

Quartus II PowerPlay功率分析器生產詳細的報告,指明哪種器件結構甚至是設計層次模塊消耗了最大的熱量。圖3列出了PowerPlay功率分析器報告。Quartus II用戶現在可以利用這些報告結果,優化設計,實現低功耗目標。

圖3. PowerPlay功率分析器報告表

S: SOPC Builder

SOPC Builder起到什么作用?

在建立一個系統時,最耗時的任務是根據系統要求集成大量的組件。SOPC Builder避免了手動系統集成任務,使您能夠將精力集中在定制用戶邏輯設計上,從而突出系統優勢。 Altera® Quartus II 設計軟件的所有版本均包括SOPC Builder 系統生成工具。SOPC Builder具有:

• 使用方便的 GUI 接口,幫助用戶高效地建立并修改系統。

• 自動集成常用的 SOPC Builder 組件、Altera知識產權 (IP)、Altera宏功能合作伙伴計劃 (AMPPSM) IP,以及定制組件內核等。

• 您可以高效地連接外部處理器和SOPC Builder可用IP庫,包括Serial RapidIO™、千兆以太網、PCI和PCI Express。

• 在您的系統中建立自己的可重用定制組件。

• 生成系統 HDL,包括針對系統組件集成需求而經過優化的系統互聯架構。

迅速推向市場——SOPC Builder應用

您可以在全部或者部分FPGA以及MAX® II CPLD 系統設計中使用SOPC Builder。采用SOPC Builder接口來選擇元件,以及元件間的連接,您會發現系統集成任務能夠在幾分鐘內完成。公共SOPC Builder應用包括:

• 構建定制Nios® II 嵌入式處理器解決方案

• 采用外設擴展定制單機處理器

• 通過PCI接口連接至ASSP以及CPU

• 構建數字信號處理(DSP)協處理器

{{分頁}}

定制Nios II嵌入式處理器解決方案

現在,您使用SOPC Builder和Altera Nios II處理器定義一個定制處理器方案,來輕松滿足您的需要(參見圖1)。

圖1. 定制Nios II嵌入式處理器解決方案

單機處理器外設擴展

采用SOPC Builder元件編輯器功能,您可以輕松實現幾乎所有外部處理器以及數字信號處理器(DSP)的接口(參見圖2)。在產生處理器的SOPC Builder元件接口時,您只需點擊幾次鼠標,便可以加入其他I/O引腳、預封裝外設以及自己的定制外設。SOPC Builder將會為您的軟件開發小組構建系統,輸出頭文件。開發小組可以采用其常用的集成開發環境(IDE),通過外部處理器來訪問外設。

圖2. CPU外設擴展

參見如何輕松實現單機處理器外設擴展:

• SOPC Builder在線演示

通過PCI連接至ASSP以及CPU

多種ASSP和處理器含有PCI接口。如果您使用Altera SOPC Builder和SOPC Builder Ready PCI MegaCore®編譯器,您將會輕松構建通過PCI實現與這些ASSP以及外部處理器進行通信的系統(參見圖3)。

圖3. PCI接口實現的ASSP以及CPU連接

DSP 協處理器

您采用SOPC Builder可以輕松構建DSP協處理器,分擔DSP器件的任務。您還可以利用Altera FPGA并行DSP處理能力,提升系統DSP處理性能。SOPC Builder元件編輯器將會幫助您構建德州儀器(TI)DSP處理器外部存儲器接口(EMIF),或者其他外設擴展以及其他處理器的外部存儲器接口(參見圖4)。

圖4. DSP協處理器

{{分頁}}

SOPC Builder接口

SOPC Builder直觀的用戶界面使您能夠輕松的選擇元件,進行參數賦值,選擇元件間的連接,生成包括互連在內的完整系統,自動生成方便軟件工程師使用的存儲器映射頭文件(參見圖5)。

圖5. SOPC Builder用戶界面

總結:最好的感受Quartus II T.I.P.S的方法就是立即安裝,相關的資源如下。

最新Quartus II軟件免費下載:www.altera.com.cn/download

Quartus II 開發軟件7.1文檔:http://www.altera.com.cn/literature/lit-qts.jsp

另外,說到TIPS, ”Show me, Guide me, Test me”, 是一個集成在Quartus II中非常好的學習工具,它可以在安裝完Quartus II 軟件后,HELP菜單中TUTORIAL欄里獲得。

評論