基于Astro工具的ASIC時序分析

引言

隨著系統時鐘頻率的提高,時鐘偏斜和干擾開始成為IC工程師重點考慮的問題。增大時序電路的時鐘頻率,減小時序電路的容差能提升未來的系統性能。低偏斜時鐘緩沖器和鎖相環時鐘驅動器將幫助設計人員設計出速度、偏斜和抗噪性能等指標滿足要求的電路系統,但必須將時鐘電路設計為一個時鐘系統,考慮時鐘分步網絡的各個方面,包括驅動器、傳輸線路和信號布線等。

時鐘偏斜

時鐘偏斜定義為在時鐘分布系統中到達各個時鐘末端(即器件內部觸發器的時鐘輸入端)的時鐘相位不一致的現象。如果時鐘偏斜超過所允許的最大值,電路的同步可能會發生失效。

偏斜主要由兩個因素造成:一是時鐘源驅動器件的偏差,例如同一個PLL輸出的不同時鐘信號之間的偏斜;另一個是時鐘分配網絡的偏斜 。由于時鐘信號驅動系統中的大量元件為了達到同步必須同時接收到時鐘信號,因此它們之間的任何時間差異都將直接影響系統性能。小的偏斜可以忽略,但大到一定程度就會嚴重影響設計的時序,因此需要在設計中盡量減小其影響。

輸出偏斜也叫做引腳到引腳的偏斜,它是指同一器件上同一躍遷的任何兩個輸出延時之間的差值。電子工程設計發展聯合協會(JEDEC)將輸出偏斜定義為單一器件輸出之間的偏斜,該器件的所有驅動輸入應連接在一起,輸出部分在同一方向切換,并驅動相同的負載。目前,高性能時鐘緩沖器中的常見輸出偏斜約為200ps。器件到器件的偏斜也稱為封裝偏斜,被定義為在相同環境下工作的兩個或多個獨立器件的任何指定輸出之間的傳送延時之差。其中,相同的環境指的是相同的輸入信號、電源電壓、環境溫度、封裝、負載等。目前的高性能緩沖器中典型的元件到元件偏斜約為500ps。

時序分析

為了保證同步系統的正常運行,所有的時序單元必須在給定的時鐘周期內正常工作。如果時序單元的總和超出了可用時間限制,系統就會發生故障。進行時序分析能夠確定可能會占用時鐘周期的所有因素并評估這些因素所帶來的影響,令設計者了解其設計的電路能夠以多快的速度運行,以及當前系統還有多大的寬裕度等。

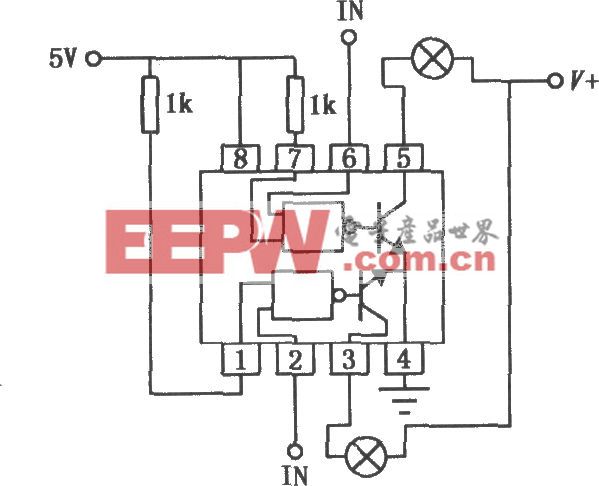

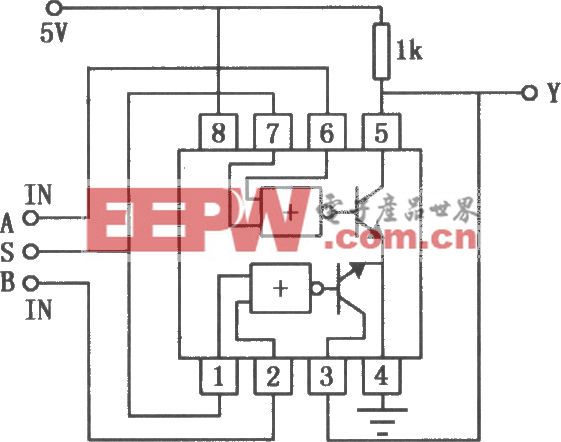

使用同步系統基本元件的簡化設計電路如圖1所示。寄存器FF1在時鐘的每個上升沿驅動,輸出Q1并將其作為組合邏輯電路C2的輸入信號。寄存器FF2使用與FF1相同的時鐘進行控制。來自于組合邏輯電路C2的數據必須先于時鐘到達,即需要一定的建立時間;而且必須要持續足夠的時間以便使寄存器FF2能夠獲得正確的輸出,即需要一定的保持時間。

解決時鐘偏斜的常用方法

時鐘偏斜是不可避免的,關鍵問題是一個系統能夠容忍多大的時鐘偏斜。通常,可允許的時鐘偏斜是由系統要求和工藝參數(例如時鐘緩沖器與寄存器的延時)來決定的。設計思路不同,得到的時鐘偏斜也不一樣。用標準單元方法設計的電路通常要比全定制電路的時鐘偏斜大一些。一般而言,一個系統中的流水線級越多,則由于時鐘偏斜導致功能錯誤的可能性越大。

在ASIC設計中,解決時鐘偏斜的方法很多。比如:按與數據流相反的方向來分布時鐘走線;控制時鐘的非交迭時間來消除時鐘偏斜;通過分析時鐘分布網絡來保證時鐘偏斜在合理的范圍內等。

上面3種方法中最好的是通過分析時鐘網絡來保證合理的時鐘偏斜。設計人員可以通過調整一些參數來控制時鐘分布網絡,以達到較好的效果。可調整的參數包括時鐘網絡的互連材料、時鐘分布網絡的形狀、時鐘驅動和所用的緩沖配置、時鐘線上的負載(扇出)、時鐘的上升和下降時間等。總之,時鐘分布網絡的目的就是使與時鐘信號相連的功能子模塊的互連線大致等長。

Astro工具的使用

Synopsys公司的Astro是在ASIC設計中流行的后端物理實現工具,是深亞微米芯片設計進行設計優化、布局、布線、計算時延的設計環境。Astro可以滿足5千萬門、GHz時鐘頻率、采用0.10um及以下工藝SOC設計的工程和技術需求,其基本流程如下:

1. 讀入網表,用晶圓廠提供的標準單元庫、Pad庫以及宏模塊庫進行映射;

2. 預布局,規定芯片的大致面積、引腳位置以及宏單元位置等粗略的布局信息;

3. 讀入時序約束文件,設置好時序建立的菜單,為后面進行時序驅動的布局布線做準備;

4. 詳細布局,力求使布線階段能順利滿足布線布通率100%的要求和時序要求;

5. 時鐘樹綜合,為了降低時鐘樹偏斜而產生由許多驅動單元組成的時鐘樹;

6. 布線,先對電源線和時鐘信號布線,然后對信號線布線,目標是最大程度地滿足時序;

7. 為滿足設計規則從而能成功制造出芯片而做的修補工作,如填充一些dummy單元等。

上面7個步驟是Astro設計的基本流程,下面針對設計中的時序偏斜對第5部分時鐘樹綜合進行重點分析。

時鐘樹綜合是時序優化處理中最重要的一步。時鐘樹綜合的目的是為了減小時鐘偏斜和傳輸延遲,通常是將最重要的時鐘放到最后來綜合,這是因為前面綜合的時鐘可能會因后面插入的緩沖器而受到影響。這些緩沖器在芯片內部應均勻分布,力求使時鐘偏斜和傳輸延遲保持在設計范圍之內。

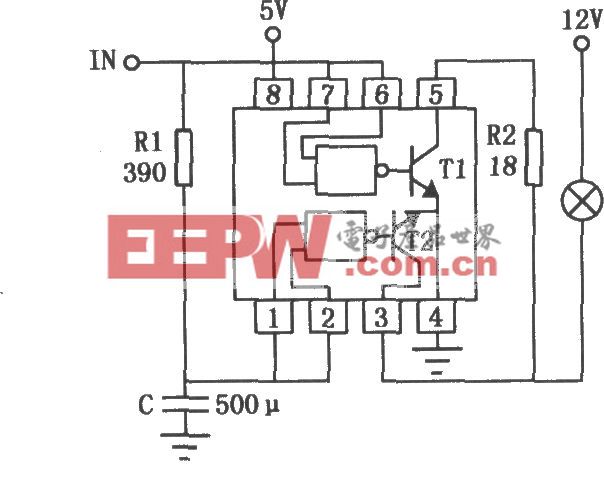

時鐘樹綜合解決時鐘偏斜的一般方法是:通過分析時鐘線路延遲,在時鐘樹中插入不同尺寸不同驅動能力的緩沖器以改變時鐘信號到達觸發器的延時,使時鐘信號能在同一時間到達各個觸發器,讓時鐘偏斜近似為零。用這種方法可以使電路盡可能不受時鐘偏斜的影響,而正確工作。時鐘樹綜合對話框和做完時鐘樹優化后常見的時鐘樹結構模型如圖2所示。

在進行完時鐘樹綜合與優化之后,可得到電路的時鐘樹偏斜報告,報告包括全局偏斜(global skew),局部偏斜(local skew)和有用偏斜(useful skew)。此時的時序應為正,否則還要進行繼續優化。

結語

對于復雜的同步系統而言,創建時序拓撲并進行時序分析是保證ASIC設計成功的基本因素。解決時鐘偏斜的方法很多,主要目的是將時鐘偏斜的影響降到最低。其實時鐘偏斜并非總是給電路帶來負面影響,我們還可以利用它來改進電路的時序,使電路工作在最優性能。

參考文獻

1 Steve Furber. ARM SoC 體系結構[M] . 田澤譯. 北京:北京 航空航天大學出版社,2003.

2 Synopsys.Synopsys Astro user guide, Clock Tree Synthesis and Clock Tree

3 Optimizations, V-2004.06

4 潘松,黃繼業. EDA 技術實用教程,北京,科學出版社,2002

5 D. Harris, M. Horowitz, and D. Liu, “Timing analysis including clock skew,” IEEE Trans. Comput.-Aided Design, vol. 18, no. 11, Nov. 1999.

6 E. G. Friedman, Clock Distribution Networks in VLSI Circuits and Systems.New York: IEEE, 1995.

評論