基于C8051F020的配電變壓器監測終端設計

摘 要:文章主要介紹了以C8051F020單片機為核心的配電變壓器監測終端的設計方案,并給出了硬件和軟件的實現方法。

關鍵詞:C8051F020;配電變壓器監測終端

引言

配電變壓器是將電能直接分配給低壓用戶的電力設備,其運行數據是整個配電網基礎數據的重要組成部分。本文設計了一種集多功能電表、無功投切控制器、采集器等功能于一體的新型配電變壓器監測終端。

硬件設計

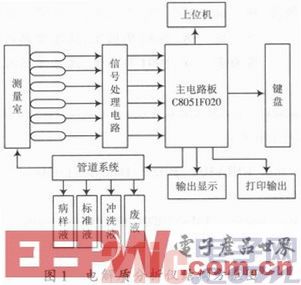

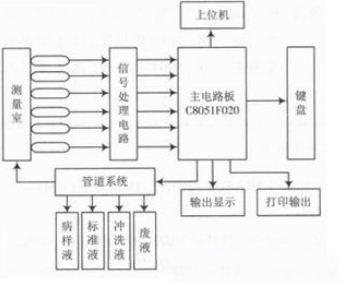

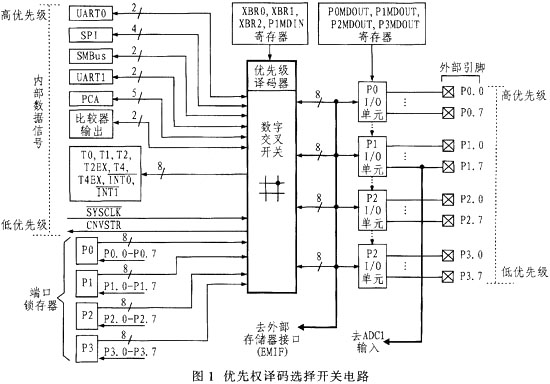

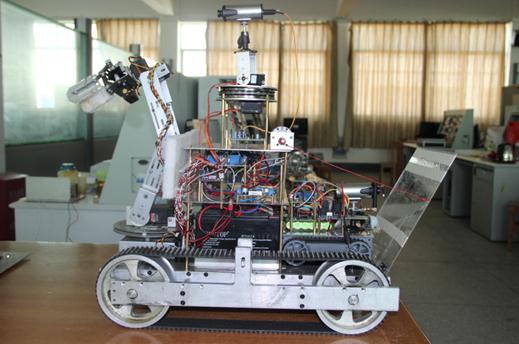

根據配電變壓器終端產品所需實現的功能要求,以單片機C8051F020為核心的硬件結構如圖1所示。

C8051F020簡介

由于配電變壓器監測終端需實現的功能較多,經反復比較,CPU選用C8051F020芯片。該芯片內置有64k Flash、4k RAM、1個SMBus/I2C、1個SPI、2個UART、5個定時器、64個通用I/O口、12位的ADC通道、電壓基準(內部、外部)、溫度傳感器等。并具有以下特點:高速的50MIPS與8051 全兼容的微控制器內核。Flash 存儲器可實現在線編程和用于非易失性數據存儲(E2PROM 的作用),工作電壓典型值為3V( 2.7V~3.3V),全部I/O、RST、JTAG 引腳均允許5V電壓輸入,工業級溫度范圍(-45 ~ +85)。片內JTAG 仿真電路提供全速非插入式(不使用在片資源)的電路內仿真支持斷點、單步觀察點、運行和停止等調試命令,支持存儲器和寄存器校驗和修改。

監控電路

選用MAX706作為微處理器監控器,主要實現上電復位、監控程序運行和掉電檢測功能。電路如圖2所示。

MAX706可獨立監視跟蹤定時器輸出。在1.6s內,如果CPU的P2.3腳電平不翻轉,則/WDO腳輸出低電平,通過/MR手動復位輸入端使/RST腳產生復位信號,以防止由于干擾使CPU死機。設跳線器的目的是為了避免在下載程序和調試時MAX706產生復位信號。

VPP為電源的掉電檢測信號,當電平降至5.5V以下時,/PFO輸出低電平,使CPU進入中斷程序進行掉電處理。CPU的P1.5腳被配置成外部中斷輸入,低電平觸發。

日歷時鐘和存儲電路

日歷時鐘芯片采用RTC4553,該芯片采用內置晶振和獨特的數據方法,大大提高了時鐘精度和可靠性。RTC4553配有串行外設通信接口,另有30

評論