基于BiFIFO的多DSP高速互連系統設計

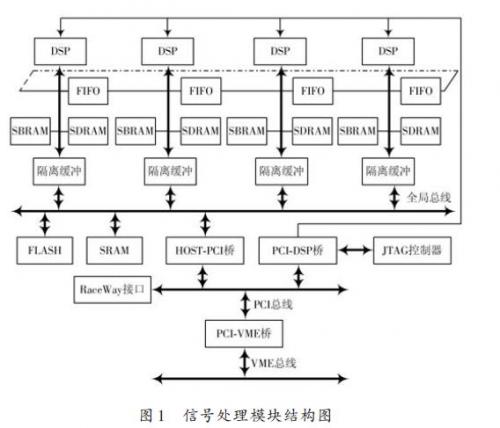

摘 要:在由TMS320C6701組成的多DSP并行信號處理系統中,DSP片間的互連性能成為系統性能的關鍵指標。本文從硬件和軟件兩個方面討論了基于BiFIFO的DSP間高速互連的設計方案。

關鍵詞:DSP互連;TMS320C6701;BiFIFO

引言

在一些應用中需要利用多DSP進行陣列運算。而在多DSP系統中,DSP間的數據交換能力已經成為系統性能的瓶頸。

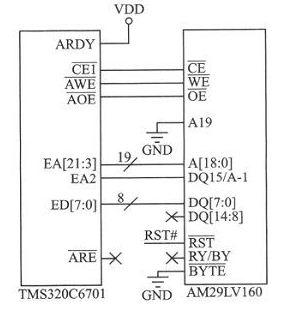

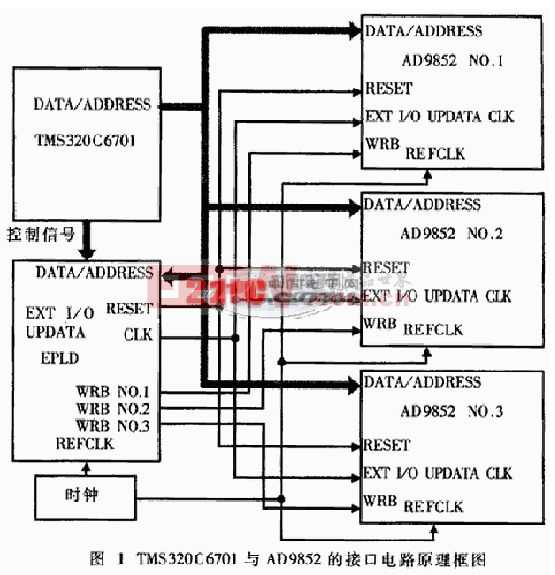

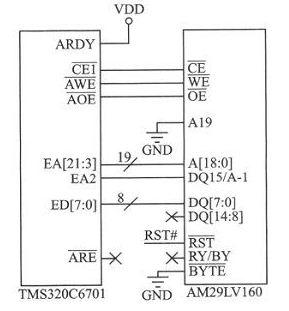

在由TMS320C6701組成的多DSP系統中,DSP互連方案主要有:通過BiFIFO(雙向先進先出存儲器)直接互連;通過DSP的HPI接口互連;通過DSP的McBSP接口互連。本文設計的高速并行信號處理板采用BiFIFO直接互連方案,該板上的兩片TMS320C6701之間通過一片BiFIFO芯片(CY7C43684)交換數據。

BiFIFO芯片CY7C43684

CY7C43684是Cypress公司推出的高速低功耗CMOS同步BiFIFO,該芯片片內有2塊獨立的16K

評論