基于ISP1362的U盤MP3播放器設計

摘 要:本文使用AT89C51SND1作為主控制器和MP3解碼器,ISP1362作為USB主機,將U盤中的MP3文件讀取出來并進行播放,實現了MP3播放器中解碼單元與存儲單元的分離。

關鍵詞:AT89C51SND1C;ISP1362;U盤;MP3播放器

播放器與存儲器的一體化設計對MP3播放器的便攜性起了關鍵性的作用,但與此同時,它又帶來了很多新的問題。比如存儲容量固定,如果想裝下更多的歌曲只能去購買新的產品,造成了巨大的浪費。另一方面,一體化又限制了MP3播放器在其它領域的應用,比如汽車電子等。于是,將存儲器與播放器分離,成為MP3的另一發展方向,也是開發這款U盤MP3播放器的意義所在。

主要芯片簡介

AT89C51SND1是ATMEL推出的基于8位C51 MCU內核的MP3解碼器芯片。它內置MP3硬件解碼器,支持48kHz、44.1kHz、32kHz、24kHz、22.05kHz及16kHz采樣頻率,具有重低音、中音、高音均衡控制和重低環繞聲效果。它可以適應市場上不同DAC的可編程音頻輸出接口,兼容PCM和I2S格式。內置2304B RAM和64KB Flash程序空間,方便用戶增加復雜的功能。并通過內置鎖相環提供MP3和音頻時鐘以及USB時鐘。

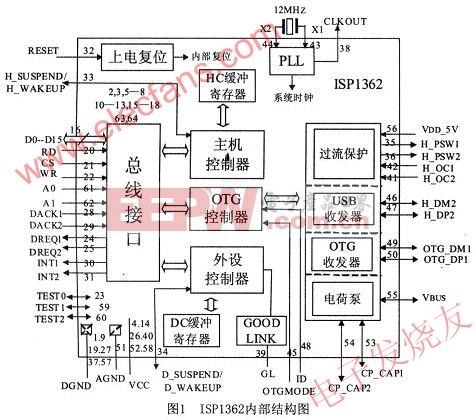

要想讀取U盤,USB主機控制器必不可少。為了將來進一步升級系統,本文選用了功能強大的USB-OTG芯片ISP1362。ISP1362在單芯片上集成了OTG控制器、高級主機控制器和外設控制器。ISP1362的OTG控制器完全兼容USB2.0以及On-The-Go Supplement 1. 0協議,主機和設備控制器兼容USB 2. 0協議,并支持12Mbps的全速傳輸和1.5Mbps的低速傳輸。

系統硬件結構

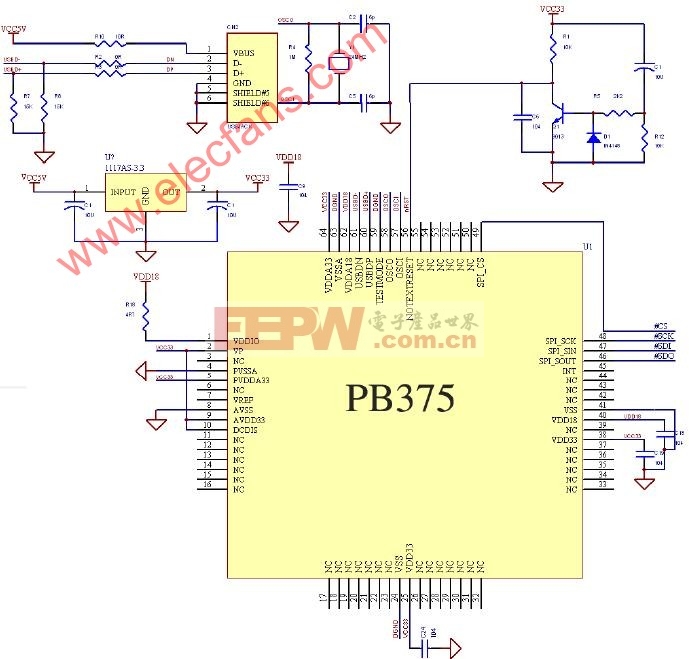

整個系統的搭建圍繞AT89C51SND1進行,如圖1所示。由于其內部具有硬件解碼器,因此電路構成并不復雜。首先由單片機控制ISP1362,將U盤中的MP3文件讀取出來,送到硬件解碼器進行解碼。解碼之后由數字音頻接口將數字信號傳送至音頻DAC CS4330,轉換之后產生音頻信號。由于DAC輸出的信號功率有限,在后端又加入了運算放大器,經過放大之后的信號就可以直接輸出給音箱或耳機等設備了。

圖1 系統框圖

AT89C51SND1是基于51內核的單片機,因此,最小系統結構非常簡單。除了傳統單片機的晶振和復位電路之外,還有PLL濾波電路和USB接口電路,如圖2所示。

ISP1362是16位總線結構,不能直接和8位單片機接口。因此,將單片機的P0和P2口一同作為數據總線接至ISP1362的16位總線上,將 、、分別接到單片機的P3.4、P3.7和P3.6,通過仿真讀寫時序控制它的數據讀取等操作。

除了這些基本的總線連接,ISP1362還需要連接一些特殊的控制引腳:

A0:用于決定控制器處于命令狀態還是數據狀態:0表示數據狀態,1表示命令狀態;

A1:用于決定控制器工作于主機還是設備控制模式:0表示處于主機控制(HC) 模式;1表示處于設備控制(DC) 模式。

接至MCU的P1.5。P1.5=0時表示處于OTG工作狀態,P1.5=1則表示處于非OTG狀態。

INT1_USB、INT2_USB分別接至MCU的INT0和INT1引腳,用以產生中斷。

ISP1362有兩個USB端口,分別是OTG端口和主機端口。因為OTG端口包含了主機功能,所以系統中使用OTG端口來連接U盤。根據USB2.0協議,USB主機需要2個15k降南呂繾瑁玂TG端口同時又可作為設備端口使用,而設備是沒有下拉電阻的。因此ISP1362提供了“軟連接”機制,通過內部的寄存器來控制電阻的連接與否。所以在硬件設計時并不需要在外部加下拉電阻。而 為開漏輸出,因此加入了一個10kW的上拉電阻R14_USB。如圖3所示。

AT89C51SND1C及

ISP1362的初始化

在開始播放MP3文件之前,需要一系列初始化操作。這些操作是通過設置AT89C51SND1C及ISP1362內部的相關寄存器來完成的。

AT89C51SND1C的初始化

為了正常播放MP3文件,首先要對主控制器AT89C51SND1C進行以下幾方面的設置。

鎖相環初始化

MP3解碼器和音頻輸出接口使用的都是內部鎖相環提供的時鐘。鎖相環的初始化是通過設置PLLCON、PLLNDIV和PLLNDIV來完成的。其輸出頻率的計算公式為:PLLclk=OSCclk

評論