集成同步解調功能的低功耗LVDT信號調理器

調節網絡元件,直到θREL絕對值低于約±3°;這樣可以改善電路對于LVDT電氣參數變化的靈敏度。

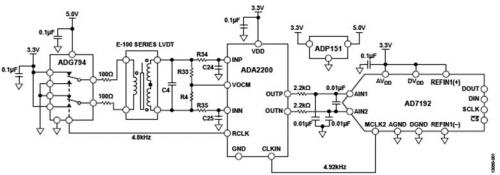

本文引用地址:http://www.j9360.com/article/276029.htmADC選擇和同步

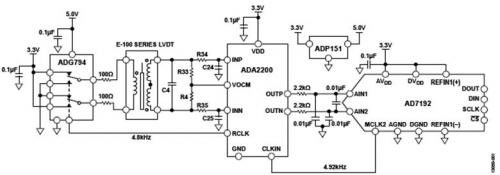

選擇AD7192Σ-Δ型ADC,因為該器件支持可配置輸出數據速率,并具有各種不同的數字濾波器輸出選項,從而允許在帶寬和噪聲之間進行權衡取舍。主時鐘輸出功能可輕松實現ADC采樣時鐘頻率與ADA2200輸出信號的鎖定。這對于優化數字濾波器性能而言是必須的。由LVDT信號確定位置所需的數值是一次激勵時鐘周期的平均值。因此,當AD7192輸出數據速率設為4.8 kHz時,即設為一個激勵時鐘周期時,可獲得所需的平均值。如果激勵時鐘周期和ADC采樣頻率未鎖定,則恢復的位置測量信息中包含錯誤。除以輸出數據速率便可有效求取多個激勵時鐘周期的平均值。

ADA2200輸出信號哪怕在LVDT核心位置固定的情況下亦含有電能,數值為激勵信號頻率的倍數。還可在頻率域中分析數字濾波器性能。AD7192具有sinc3或sinc4傳遞函數,該傳遞函數在輸出數據速率的倍數處歸零。這些頻率分量是雜散誤差的來源。通過將ADC的輸出數據速率設為激勵信號頻率(或激勵頻率的約數)便可抑制輸出雜散。如果激勵時鐘周期和ADC采樣頻率未鎖定,則雜散將不會落在傳遞函數的零點。

用于性能分析的用戶軟件

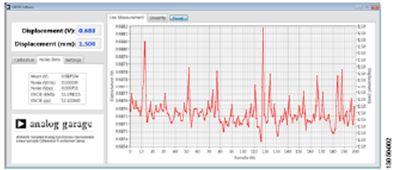

該電路支持圖形用戶界面,可方便地進行板上的器件配置,并評估電路性能。該軟件的選項卡可執行電路校準和器件配置,以及顯示噪聲性能、線性度性能和實時位置測量。

圖2.用戶軟件屏幕截圖

噪聲分析

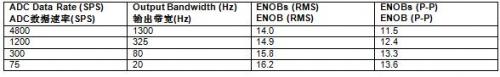

該電路的輸出噪聲是ADC輸出數據速率的函數。表1顯示數字化數據相對于ADC采樣速率的有效位數(ENOB),假設滿量程輸出電壓為2.5 V.該電路的噪聲性能與LVDT核心位置無關。

表1.噪聲性能與帶寬的關系

如果ADA2200輸出噪聲與頻率無關,則預計有效位數將在輸出數據速率每4次折疊下降時增加一位。ENOB在較低輸出數據速率下的增加放緩是由于輸出驅動器的1/f噪聲所導致的;該噪聲在較低的輸出數據速率下成為噪底的主要成分。

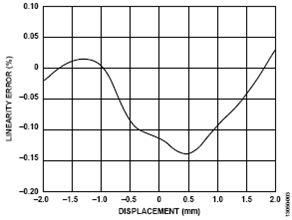

線性度測試結果

首先在±2.0 mm核心位移處執行一次兩點校準即可測量線性度結果。由這兩次測量結果可確定斜率和失調,從而實現預期直線擬合。然后,在±2.5 mm滿量程范圍內測量核心位移。從預期直線擬合數據中減去測量數據即可確定線性度誤差。

圖3.位置線性度誤差與LVDT內核位移的關系

測得的數據顯示電路性能優于E-Series LVDT數據手冊中指定的線性度性能。

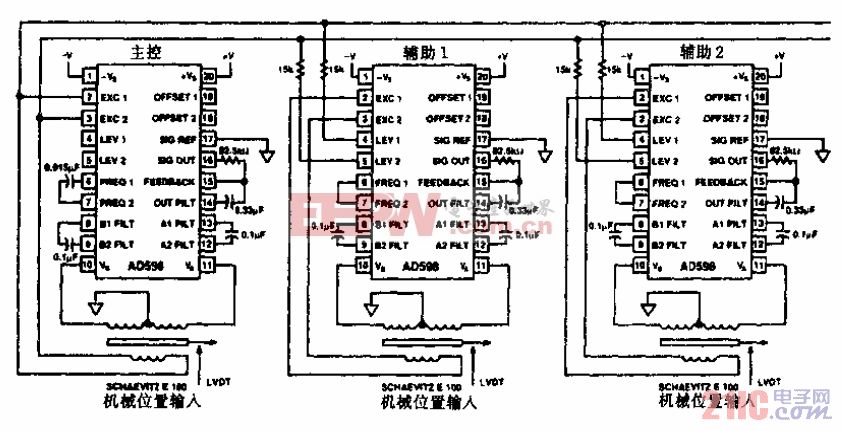

多LVDT同步工作

很多應用都會近距離使用多個LVDT.若這些LVDT以相似的載波頻率運行,雜散磁耦合可能導致拍頻。產生的拍頻可能會影響這些條件下的測量精度。為避免這種情況,所有LVDT必須同步工作。

通過讓器件同時退出復位狀態,可同步多個ADA2200器件。ADA2200在RST引腳解除置位之后的第一個CLKIN上升沿時退出復位模式。因此,從單一源驅動所有ADA2200 CLKIN引腳以及所有RESETB線路便足以確保器件同步工作。避免在CLKIN上升沿附近對RESETB解除置位,以防器件在不同時鐘沿上復位。可監控ADA2200器件的RCLK輸出,確保ADA2200器件正確同步。

常見變化

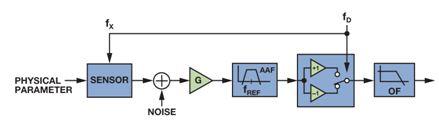

在某些系統中,可能需要使用SAR ADC,而非Σ-Δ型轉換器。這些情況下,ADC轉換時鐘必須與ADA2200更新速率同步。如前所述,ADA2200輸出會在激勵頻率的倍數處含有雜散。這些雜散可通過移動平均濾波器或級聯多個移動平均濾波器加以抑制。移動平均濾波器易于實現,且具有出色的時域特性。若要完全抑制雜散,則移動平均樣本大小必須等于8個樣本的整數倍。

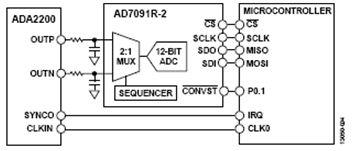

圖4顯示了ADA2200連接至AD7091R-2,后者是一個超低功耗、雙通道、12位SAR ADC.使用一個雙通道ADC,因而ADA2200的OUTP和OUTN輸出可順序采樣。由于ADA2200輸出為分立式時間樣本,通過對兩個順序輸出樣本執行減法操作(即VOUTP - VOUTN)便可實現差分測量。

圖4.采用雙通道SAR ADC進行差分采樣

SYNCO信號在每個ADA2200輸出采樣周期內變為有效。SYNCO可用來中斷微控制器,以便獲取一對ADC樣本(對OUTP和OUTN采樣)。在上述示例中,采樣周期等于激勵時鐘頻率乘以8(或38.4 kHz);因此,ADC采樣速率為76.8 kSPS.

模擬信號相關文章:什么是模擬信號

濾波器相關文章:濾波器原理

濾波器相關文章:濾波器原理

模數轉換器相關文章:模數轉換器工作原理

低通濾波器相關文章:低通濾波器原理

分頻器相關文章:分頻器原理 電荷放大器相關文章:電荷放大器原理

評論