PCB特性影響電源分配網絡(PDN)性能

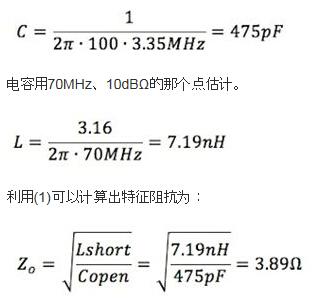

我們可以使用圖4中的示波器測量結果近似計算PCB的特征阻抗。電容是用標記M3估計的。

本文引用地址:http://www.j9360.com/article/275992.htm

另外,特征阻抗可以看作是開路阻抗和短路阻抗的交叉點,發生在近似11.5dBΩ或3.76Ω點。

也可以使用(4)和帶2.7Ω端接電阻的近似峰值阻抗(14.5dBΩ)計算PCB的特征阻抗。

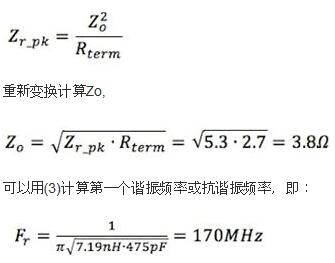

用3.6Ω的端接電阻重復進行測量,如圖5所示。

圖5:用3.6Ω代替2.7Ω端接電阻對同一塊PCB進行測量(紅色)。注意,在采用3.6Ω的端接電阻后,只有少量峰值指示其特征阻抗稍大于3.6Ω。

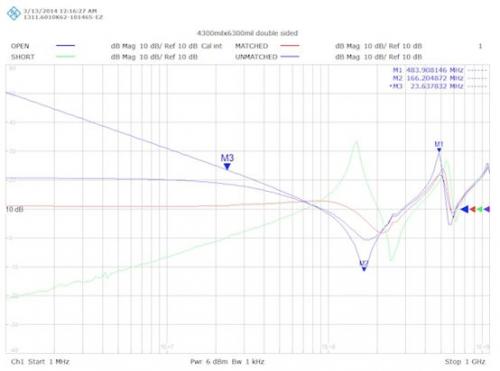

對PCB進行仿真并與圖5進行比較,結果如圖6所示。

圖6:PCB仿真結果與圖5所示的測量結果進行比較。

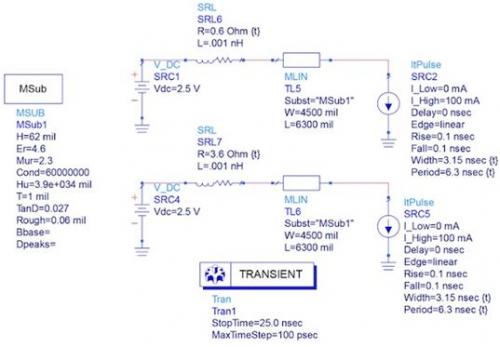

最后,使用電源端的0.6Ω和3.6Ω源阻抗并在PCB諧振頻率點仿真動態瞬時響應。仿真模型見圖7,仿真結果見圖8.

圖7:用0.6Ω和3.6Ω源阻抗代表穩壓器輸出阻抗,在諧振頻率點進行動態負載瞬時ADS仿真。

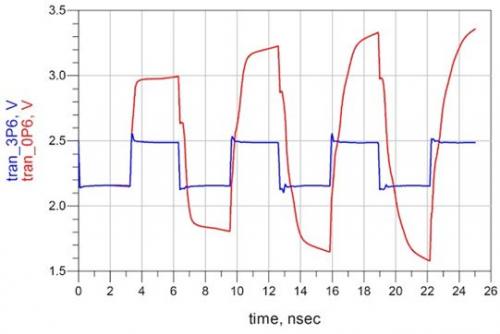

圖8:瞬時響應仿真結果表明,0.6Ω較低源電阻(紅色)的瞬時響應比匹配的3.6Ω源電阻(藍色)具有大得多的電壓偏移。

小結

本文討論了幾種確定電路板特征阻抗的方法,并用仿真模型定義了PCB特征與PDN性能之間的重要關系。在經過實際測量后,關系得到了確認。

可以通過觀察第一個缺陷是諧振點還是抗諧振點來判斷PCB阻抗是否大于或小于端接阻抗,端接阻抗是否大于PCB阻抗。

這些結果清晰地表明,為了優化PDN性能,必須使PCB層阻抗與穩壓器的輸出阻抗相匹配。最好是使PCB層阻抗等于穩壓器的輸出阻抗,如果不可能實現的話,PCB阻抗應該低于穩壓器輸出阻抗,以便更好地包含與峰值阻抗最大值相關的峰值偏移。

評論