【從零開始走進FPGA】美好開始——我流啊流啊流

2. 仿真必備的知識

本文引用地址:http://www.j9360.com/article/268641.htmAltera_Modelsim仿真資料:http://www.chinaaet.com/lib/detail.aspx?id=86257

四、配置FPGA

1. 配置綜合

配置引腳簡單的說就是通過軟件的設置,將FPGA內部邏輯信號映射到IO上,具體有下面幾種方法:

(1)在Assignments-Pin Planner中對應IO手動輸入IO引腳

(2)Quartus II Tcl Console 手動輸入,輸入的格式為:“set_location_assignment PIN_28 -to clk”

(3)Tcl Scripts,通過調入tcl 文件來進行映射

(4)在Assignments-Import Assignments,通過調入(2)格式的文件來進行映射。

后面兩種方法具體步驟可見網友“小時不識月”的網頁教程:http://www.cnblogs.com/yuphone/archive/2010/01/18/1650612.html

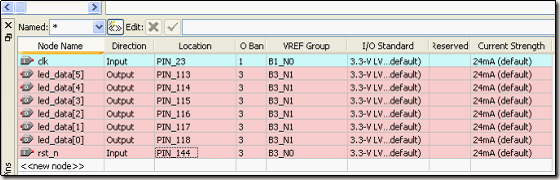

配置好查看Quartus II Pin Planner,如下圖所示:

配置完引腳在進行綜合,就少了上述提醒沒有進行引腳配置的2個警告。

注意1:對于Quartus II 中引腳配置的方法,若用最原始的第一種GUI手動輸入配置,需要第一次編譯后讓軟件在Pin Planner生成IO,然后再GUI下手動配置;若用其他三種方法,可以在第一次編譯以前,用命令輸入配置信息,在Quartus II 編譯后,自動識別映射信息,達到同樣的效果。

注意2:對于系統及的FPGA設計,由于工程之大,引腳之多,一般編譯綜合需要耗費很大的時間,因此一般采用不采用第一種方法,而且在第一次編譯以前事先導入映射信息。

2. 目標板下載模式

總而言之,Quartus II 軟件只是個GUI的 用戶終端,用來設計代碼,綜合FPGA邏輯電路,最終的目的,是通過USB Bluster、并口或者其他途徑下載到目標板。具體有以下幾種:

(1)配置FPGA——JTAG Mode

所謂配置FPGA就是將sof文件電路配置FPGA的SRAM(FPGA是基于SRAM格式的),在不掉電的情況下進行現場配置,驗證。此方式是通過JTAG接口下載的。

(2)燒錄EPCS——Active Serial Programming

所謂燒錄EPCS是生成的代碼信息燒錄到存儲芯片EPCS中,通過配置信號或者重新上電,配置FPGA SRAM;由于EPCS flash結構,因此EPCS中的掉電不丟失(類似于CPLD)。燒錄EPCS有兩種方法,如下

a) 通過ASP接口下載pof文件

b) 通過JTAG接口下載jic/jam文件,jic/jam文件由Quartus II 軟件對sof文件進行轉換后得到。

(3)Passive Serial并口下載

(4)In Socket Programming下載

以上兩種模式,由于應用不是很廣泛,在此不做過多闡述。

綜上說明,在成本敏感,或者電路板空間苛刻的情況下,完全可以舍去ASP接口,而用JTAG來替換。考慮到Altera設計了兩種接口的原因,是給用戶更大的選擇性,特殊場合下,可以只存在ASP接口,只進行一次燒錄,而不用JTAG接口進行測試。

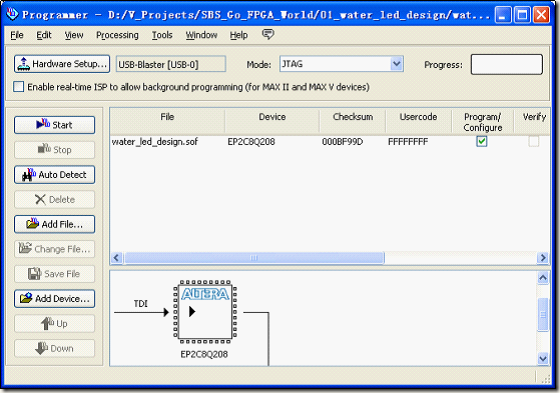

3. JTAG的下載

(1)在工具欄打開或者菜單欄Tool打開Programming

(2)若沒找到Hardware,在Hardware Setting中找到USB Bluster。

(3)選擇JTAG Mode

(4)若沒有自動加載sof文件,點擊Add File導入該工程的sof文件

(5)最后點擊Start,等待下載完畢,如下圖所示:

fpga相關文章:fpga是什么

c++相關文章:c++教程

評論