基于FPGA的SOC設計與實現

在圖4中顯示的是FS2工具的用戶界面,設計中用到的八條指令,分別是:1>、2>、3>……8>,其中指令1>、2>用來配置片外Flash芯片;指令3>用來選擇將要擦寫的存儲空間,由圖中可知,本設計中要進行的讀寫操作 的存儲空間是Ox00000000-0x003FFFFF;指令4>用來對Flash指定的存儲空間進行擦除操作;指令5>用來把已經準備好的二進制文件寫到上述存儲空間中,設計中使用的二進制文件名是QUICK.HEX;指令6>是用來顯示指定存儲空間中的內容,從圖中可看出,寫到存儲空間Ox00000000-0x0000003F的內容是18、FO、9F……、12、E3;指令7>執行對上述存儲空間寫入的數據的擦除操作;指令8>顯示上述存儲單元擦除后的內容。

本文引用地址:http://www.j9360.com/article/264101.htm

?

圖4 片外Flash的擦寫演示過程

通過對上述過程的分析可知,所搭建的SOC系統可準確實現片外Flash的擦寫操作,進而說明了該系統的準確性。

3.2 搭建的系統對外設接口的讀寫操作

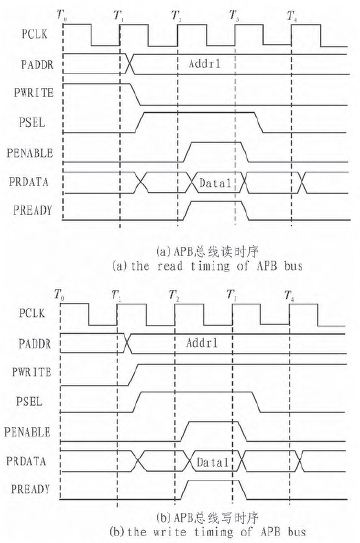

本測試在遵循ARM7先進外圍總線APB的讀寫時序的前提下,定制用戶邏輯外設PIO,通過該系統對PIO接口進行讀寫操作來進一步驗證設計的準確,驗證中的用到的APB總線的讀寫時序如圖5。

?

圖5 APB總線的讀寫時序

下面將主要遵循系統中先進的外圍總線APB的讀寫時序,首先采用硬件描述語言和C代碼,定制八位的用戶邏輯外設PIO,然后將PIO的輸入端口接到開關Switch0一Switch7,輸出端口接到八個發光二極管Led0一Led7,通過軟硬件調試,使八位開關的輸入電平顯示到八個發光二極管上,以此來進一步驗證設計中搭建的SOC系統的準確,針對上述過程及要求,為了更直觀地展示驗證結果,制作了簡單的實驗板,當開關鍵在高電平時,發光二極管變亮,否則,發光二極管不亮。其中定制用戶邏輯外設的主要步驟如下:

1)規劃元件的硬件功能;

2)使用硬件描述來描述硬件邏輯;

3)單獨驗證元件的硬件功能;

4)描述寄存器的C頭文件來為軟件定義硬件寄存器映像;

5)將元件集成到ARM7系統中,使用ARM7來測試寄存器的訪問是否正確,并為該元件編寫軟件驅動;

6)執行系統級的驗證等。

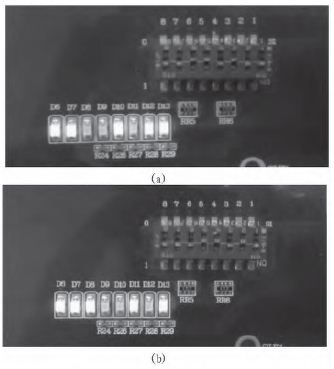

圖6是在Aetel公司的調試軟件Sofleonsole和實驗板上的實際調試結果。

?

圖6 調試結果

由圖6顯示的調試結果可知,八位開關Switeh0-Switeh7的輸入分別是11001011和11100101,這個和八個發光二極管Led0-Led7的輸出結果一致,由此進一步驗證了設計的準確性。

4 結束語

本文通過對基于ARM7的SOC系統的設計,介紹了一種Flash結構的FPGA器件及其片上系統的設計方法,進而給出了兩種驗證該片上系統準確性的方法,通過實際驗證,該系統不僅能準確進行片外存儲器的擦寫,而且可以準確進行外設接口的讀寫的操作,由此驗證了設計的準確性。文中所搭建SOC系統,可以與符合ARM公司的AHB2.0協議的北斗基帶芯片無縫連接,在北斗接收機的設計、測試中有重要的參考價值。

評論