C波段寬帶捷變頻率綜合器設計

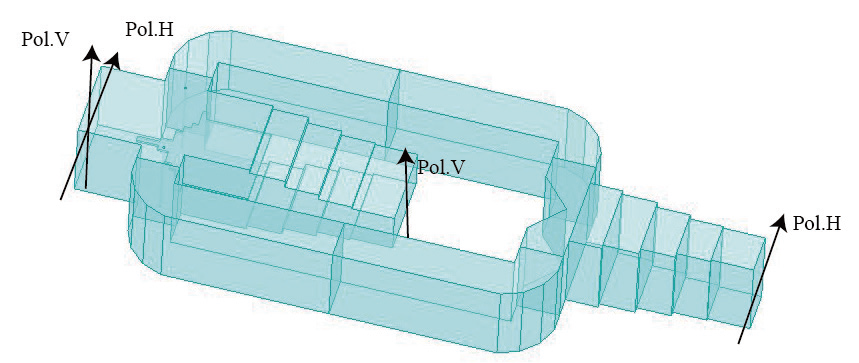

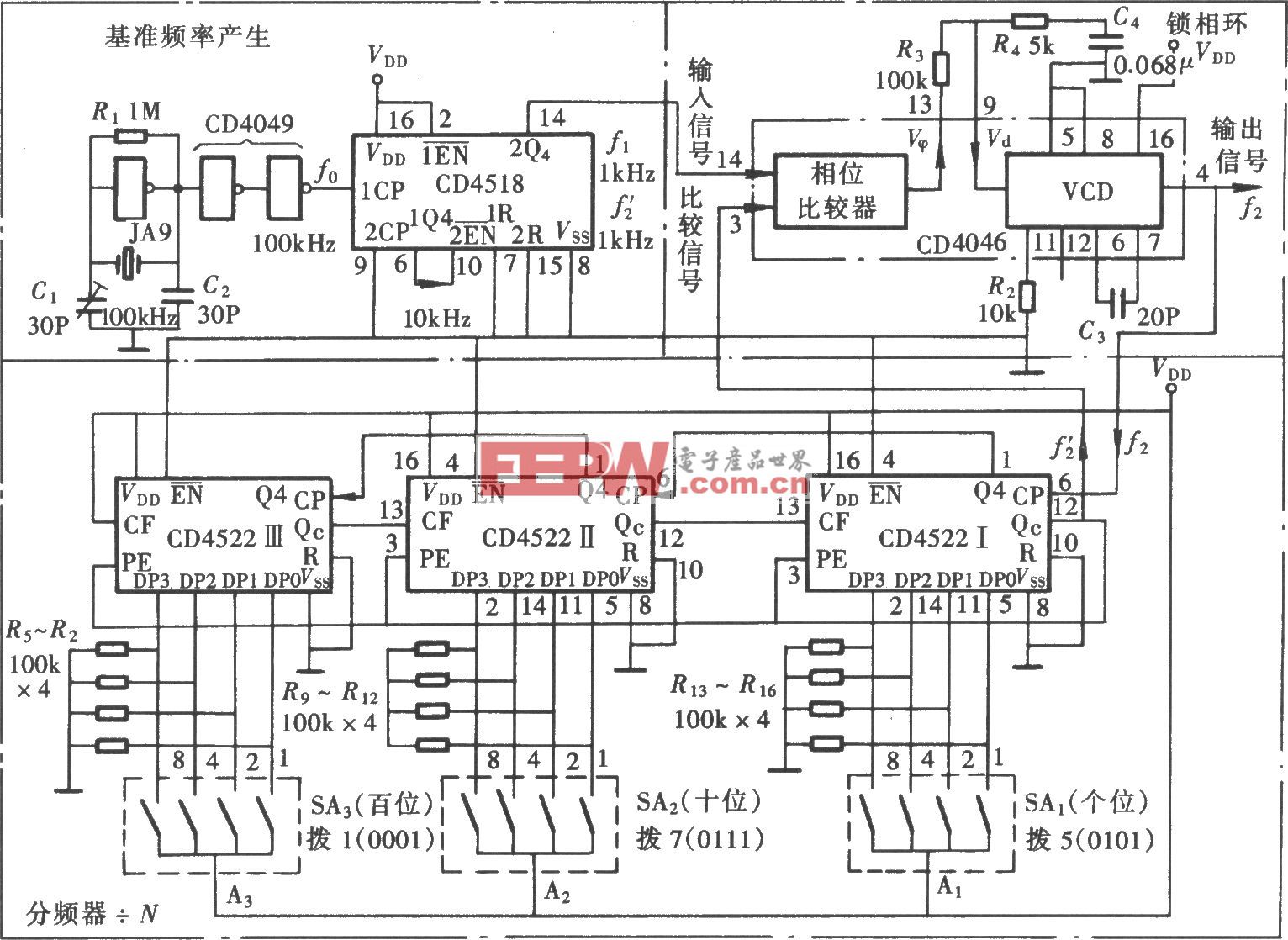

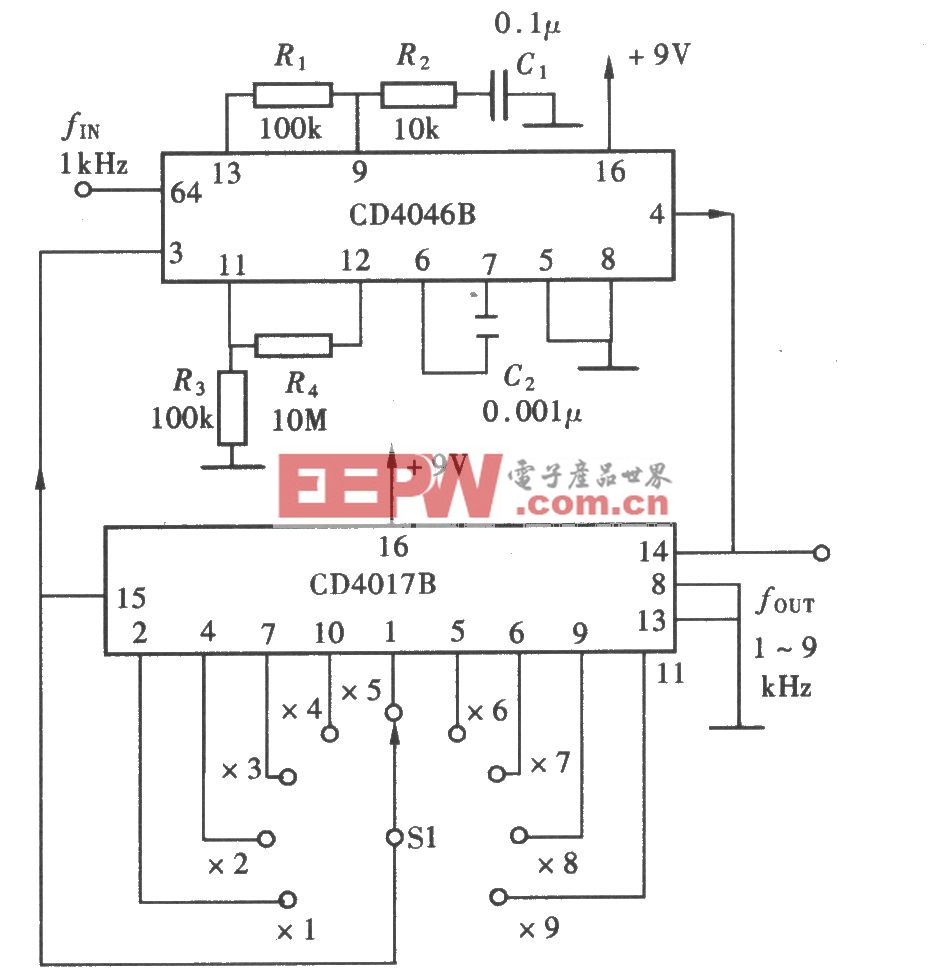

編者按: 摘要:本文介紹了一種C波段寬帶捷變頻率綜合器的設計方法,采用直接數字頻率合成器(DDS)實現頻率捷變,采用倍頻鏈路擴展輸出帶寬,通過與鎖相環(PLL)合成產生的本振信號混頻將輸出頻率搬移到C波段。論述了DDS時鐘電路、倍頻鏈路以及混頻部分的設計方法,并給出了達到的主要技術指標和測試結果。

引言

頻率合成器是現代通訊系統必不可少的關鍵電路, 是電子系統的主要信號源,是決定電子系統性能的關鍵設備。隨著系統對頻率源的頻率穩定度、頻譜純度、頻率范圍和輸出頻率個數的要求越來越高,高穩定、低相位噪聲、

實現的性能指標如下:

本文引用地址:http://www.j9360.com/article/263364.htm輸出頻段:6.5125~6.7375GHz、6.5875~ 6.8125GHz、6.6625~6.8875GHz、6.7375~6.962GHz

頻率步進:1Hz

跳頻速度:≤100ns

雜散抑制:≤-58dBc

以PLL產生本振為6.075GHz時為例,該路最終應輸出6.5875~6.8125GHz頻率,用頻譜儀測量該路最終混頻輸出的頻譜如圖5所示。

該路輸出頻段內最大雜散點如圖6所示,此時雜散抑制為-60dBc左右。

4 結束語

本文采用DDS結合倍頻和上變頻技術的方案實現了C波段寬帶捷變頻率綜合器,該頻率合成器具有頻率切換速度快,步進小,工作頻帶寬,輸出雜散低等特點,具有較高的工程應用價值。

參考文獻:

[1]高玉良.現代頻率合成與控制技術[M].北京:航空工業出版社,2002

[2]張大鶴,紀學軍,李青平.小步進捷變頻率合成器設計技術[J].無線電工程,2009,39(6):43-46

[3]李昂.X波段連續波雷達收發前端的設計與實現[D].成都:電子科技大學,2013

[4]陳之光,陶駿,田野,等.某型高雜散抑制捷變頻率合成器研制[J].壓電與聲光,2013,35(1):132-135

[5]李軍.X 波段微波倍頻器的研制與一種頻率源的設計[D].成都:電子科技大學,2004

評論