利用普通數字存儲示波器排除嵌入式系統數字類故障

雖然目前的服務器和PC越來越青睞先進高速處理器,但是低檔的20或30MHz處理器在現實生活中還在發揮作用。盡管這些粗笨的微處理器設計陳舊,已有多年歷史,它們卻依然在機械、消費類電子及車用電器中占有一席之地。

這些嵌入式處理器及其應用有什么共同點呢?歸納起來有這樣幾個明顯特征:第一,這類處理器經過很多產品充分驗證,人們都非常了解,而且開發可得到廣泛支持,易于設計;第二,與現有高端方案比較,其時鐘速率相對較慢,總線速率也很慢;第三,應用系統(從自動售飲料機到航空電子設備)必須要有很高的可靠性;最后,成本(包括設計、制造和維護費用)必須盡可能低。

還有一個特性值得注意,即目前存在這樣一個穩定的發展趨勢,這些嵌入式器件和總線時鐘速率都在不斷提高,倒不是說要趕上速度最快的服務器,而是將朝“短時鐘周期”器件方向發展,時鐘速率比以前快5~6倍。和過去的處理器相比,新器件具有相同引腳和功能,但能在給定時間內做更多工作,它可執行更多指令周期完成更復雜工作而不會拖慢整個系統運行速度。這一點尤其對軟件開發商有利,因為耗時的代碼優化不再顯得重要,新產品將會更快更便宜地推向市場。

進行基本數字檢查的普通示波器帶寬已比以前翻了一番,達到200MHz,而且一些非常有用的“高檔”測量特性如高級觸發、快速傅立葉變換(FFT)分析及彩色顯示等也都相繼加入到低檔儀器中。如今的設計人員在面對民用產品嵌入式處理器時,也都能用得上數字式故障檢測方案。

帶寬決定應用

不久前生產的處理器和十年前生產的同一器件相比,多了一個隱蔽的“性能”,即信號邊緣轉換速度更快。從15年前生產這些產品所使用的CMOS工藝到5年前開發的快速5V工藝,邊緣轉換速度提高了約3倍,很多新設計都用這種最快的5V工藝,甚至有的還進一步降低內核部分電壓而只在外圍采用5V,對后者而言還能達到更快時鐘速率,這種速度加快是硅片特征尺寸縮小所帶來的副產品。

邊緣速度更快通常是件好事,可減少系統內的時延、設置時間及沖突等問題,但傳播延遲更短(大部分是由于CMOS更快邊緣速率所造成)也會產生不利影響。當這類延遲越來越短時,通常取決于地址線邏輯和總線控制線間延遲的地址解碼余量將遇到更多麻煩。因此設計人員需要知道并了解這些邊緣狀況、越來越窄的瞬時現象及高速轉換時可能出現的其它脈沖特性。

在為一個含20MHz嵌入式處理器的數字設計選擇DSO時,人們可能會認為用帶寬50MHz或100MHz儀器對付這項工作完全綽綽有余。當然對一些基本故障檢測,諸如有沒有信號或者時序和同步是否準確之類的問題,確實是這樣的,但其它細節可能就不那么明顯。

具有較高帶寬的DSO比低帶寬儀器能更加深入地了解信號特性,因為示波器上升時間已成為確定被觀察信號質量的因素之一,有公式如下:

測得上升時間=√(示波器上升時間)2+(信號上升時間)2

在低帶寬觀察時顯得“正確”的脈沖可能會在前沿有一個幅值偏差,使其表現像兩個脈沖;或者總線輸出上的一個很窄瞬時信號可能完全注意不到,導致后面器件輸入不穩定。如上面公式所示,一個200MHz的DSO可以捕捉到100MHz儀器看不到的細節。

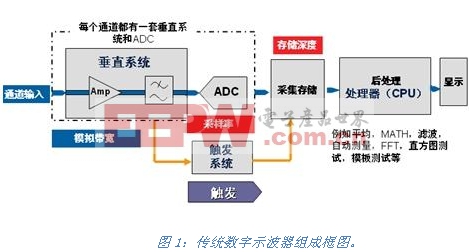

DSO帶寬大的好處不僅僅限于觀察信號邊緣,使用高帶寬儀器時,接地反彈、噪聲、串擾及其它許多偏差都更易于觀察到,也更不容易忽略。帶寬越高,信號再現就越準確。圖1顯示了同一信號在60MHz和200MHz帶寬示波器上看到的不同情形。

用條件觸發檢測時序問題

在數字存儲示波器中,觸發條件選擇是一個重要但有時卻不太為人所知的省力工具,它使DSO觸發符合所指定的條件。如同顯示波形一樣,條件觸發是嵌入式系統檢測的一個基本工具,很多人使用噪聲抑制(通常增大觸發滯后)來限制短脈沖,并用各種帶寬限制選擇所需要的信號。

評論