高密度封裝技術推動測試技術發展

自從表面貼裝技術(SMT)開始逐漸取代插孔式安裝技術以來,線路板上安裝的元件變得越來越小,而板上單位面積所包含的功能則越來越強大。

就無源表面貼裝元件來說,十年前鋪天蓋地被大量使用的0805元件,今天的使用量只占同類元件總數的大約10%;而0603元件的用量也已在四年前就開始走下坡路,取而代之的是0402元件。目前,更加細小的0201元件則顯得風頭日盛。從0805轉向0603大約經歷了10年時間。無疑,我們正處在一個加速小型化的年代。

再來看看表面貼裝的集成電路。從10年前占主導地位的四邊扁平封裝(QFP)到今天的倒裝芯片(FC)技術,其間涌現出五花八門的封裝形式,諸如薄型小引腳封裝(TSOP)、球型陣列封裝(BGA)、微小球型陣列封裝(μBGA)、芯片尺寸封裝(CSP)等。縱觀芯片封裝技術的演變,其主要特征是元件的表面積和高度顯著減小,而元件的引腳密度則急驟增加。特別是BGA技術,已成為現代高密度IC封裝技術的主流,如圖1所示的NVIDIA公司的GeForce FX圖形芯片(GPU)含有1152個焊腳,是同等尺寸大小QFP所容納引腳數的3-4倍。但高I/O數也給傳統電路接觸測試(如ICT)帶來挑戰,同時BGA焊點隱藏在封裝體下面,無法進行人工目檢。。

表面貼裝元件尺寸的不斷縮小和隨之而來的高密度電路安裝,對測試帶來了極大的挑戰。傳統的人工目檢即使對于中等復雜程度的線路板(如300個元件、3500個節點的單面板)也顯得無所適從。

曾經有人進行過這樣的試驗,讓四位經驗豐富的檢驗員對同一塊板子的焊點質量分別作四次檢驗。

結果是,第一位檢驗員查出了其中44%的缺陷,第二位檢驗員和第一位的結果有28%的一致性,第三位檢驗員和前二位有12%的一致性,而第四位檢驗員和前三位只有6%的一致性。

這一試驗暴露了人工目檢的主觀性,對于高度復雜的表面貼裝電路板,人工目檢既不可靠也不經濟。而對采用微小球型陣列封裝、芯片尺寸封裝和倒裝芯片的表面貼裝線路板,人工目檢實際上是不可能的。

不僅如此,由于表面貼裝元件引腳間距的減小和引腳密度的增大,傳統的電路接觸式測試受到了極大限制。據北美電子制造規劃組織預計,在2003年后利用在線測試對高密度封裝的表面貼裝線路板檢測將無法達到滿意的測試覆蓋率。以1998年100%的測試覆蓋率為基準,估計在2004年后這測試覆蓋率將不足50%,而到2010年后,測試覆蓋率將不足10%。另外在線測試技術還存在的背面電流驅動、測試夾具費用和可靠性等問題的困擾,種種跡象表明這一技術的發展已走到了盡頭。

柳暗花明: 光學檢測技術帶來測試新體驗

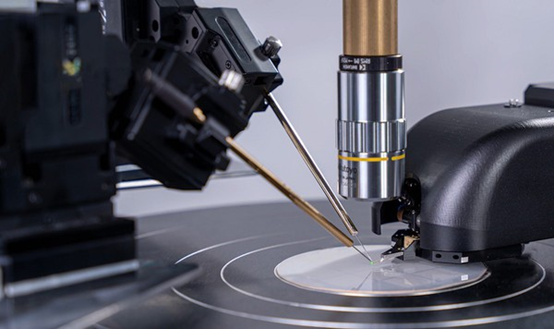

技術的發展絕不會因為上述困難就停滯不前,測試檢驗設備制造商推出了像自動光學檢測(Automatic Optical Inspection,簡稱AOI)設備和自動X射線檢測(Automatic X-ray Inspection,簡稱AXI)設備等這樣的產品來應對挑戰。事實上,這兩種設備在被大量用于線路板制造工業以前,就已經在半導體芯片制造封裝過程中得到了廣泛的應用。不過,它們還需要進一步的創新才能真正應對由表面貼裝元件小型化和高密度線路板帶來的測試困難。

評論