應用高帶寬示波器表征GDDR5數據抖動,確保有效的數據傳輸

抖動對GDDR5數據的影響

GDDR5 SGRAM傳輸數據使用自由運行差分前向時鐘(WCK/WCK#),并在前向WCK的兩個邊沿上分別寄存并驅動輸入和輸出數據,以用于讀和寫訓練。讀/寫訓練支持數據定時和幅度電平裕量優化。盡管JEDEC標準沒有相關規定,普遍觀點認為表征抖動特性是在如此高的數據速率傳輸條件下的重要測量任務。導致GDDR5系統產生抖動的原因,例如碼間干擾(ISI)、串擾、占空比失真(DCD)等,這些都會限制圖形卡以及存儲器控制器與DRAM接口的性能。

抖動是指信號跳變邊沿與理想時間的偏差。隨著數據速率的提升,定時裕量日趨嚴格,甚至每一皮秒的裕量都變得更為重要。高速據速率時代,微小的抖動都可能導致讀寫數據的數據有效窗口關閉,最終增加比特誤碼率和數據采樣誤差。

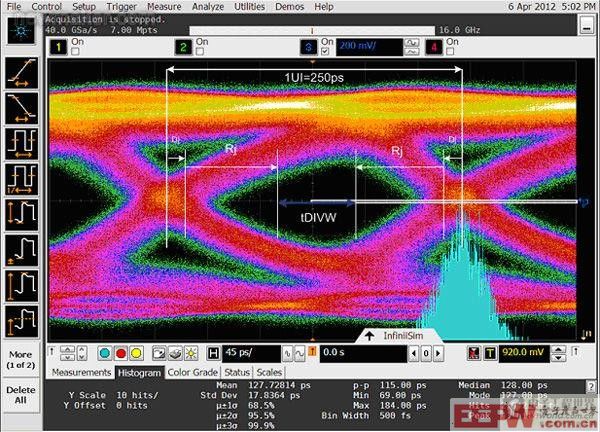

在高數據速率(例如5Gb/s或以上)條件下,數據有效窗口非常小。系統中的噪聲或相鄰電信號的串擾甚至電磁干擾都極易造成信號失真和信號完整性問題,導致數據采樣誤差。實時眼圖可以提供眼圖高度和眼圖寬度測量以檢查信號完整性并預估數據有效窗口。但是,僅使用實時眼圖測量數據眼圖無法獲得完整的有效數據窗口分析和比特故障率預測。圖 1是一個具有一百萬單位間隔(測得的單位間隔)的寫數據眼圖。一百萬單位間隔的初始測量得到200ps的數據輸入有效窗口。確定性抖動(DJ)線和隨機抖動(RJ)線顯示了長時間累積的抖動效應和實際數據輸入有效窗口,即一萬億單位間隔(1e-12比特誤碼率或BER)后的tDIVW。確定性抖動通常有界、可預測并且與數據碼流相關聯,例如碼間干擾和占空比失真。隨機抖動通常為高斯抖動且無界。同其它高斯分布一樣,該分布的峰峰值將隨著數量的增加而增大。因此,總體抖動是隨機抖動乘以BER倍數因子再加上確定性抖動與。注意,圖示是寫數據的數據輸入有效窗口。您可以發現,抖動BER測量計算非常重要,是總抖動統計測量的重要組成部分,可以幫助您了解設計的數據有效窗口結果并預測設計中的錯誤率。另外,了解抖動分量和抖動源可支持設計人員降低設計抖動,確保更精確的數據傳輸。

圖1:顯示確定性抖動和隨機抖動對數據有效窗口影響的GDDR5寫數據眼圖

GDDR5系統設計人員面臨的最大挑戰是分離讀和寫數據以進行抖動測量。讀和寫數據使用相同的數據路徑,但它們對設計有各自不同的重要意義。許多設計人員使用混合信號示波器觸發命令協議,以獲得相應的讀和寫數據。使用混合信號示波器分離讀和寫數據需要訪問WCK和DQ以及時鐘、CS#、RAS#、CAS#和WE#等信號的能力。此方法十分繁瑣,因為信號接入會受到電路板狹小空間的限制,并且部分情況下連接多個信號可能導致嚴重的探頭負載問題。

高帶寬示波器可用于抖動測量。數據分離技術只需將CAS#、WE#、WCK和DQ連至示波器標配的4個模擬通道,以識別讀和寫命令。當CAS#切換至低電平,表明現在是某個列地操作址命令。在此條件下,命令的范圍將縮小,可能是取消選定、MRS、讀、寫、刷新或自刷新入口。如果WE#與CAS#同時設為低,則可能的命令僅包括取消選定、MRS和寫數據。通過測量可確定寫延遲并且可以使用寫延遲從取消選定與MRS中分離寫周期和。器件在取消選定命令狀態時,數據必須保持在ODT狀態。對于MRS命令,在MRS命令執行后延遲10ns會輸出廠商ID 。因此,CAS#和WE#設為低時,在寫延遲后的數據信號是寫數據。在WE#高而CAS#低跳變時,表明是取消選定、讀、刷新和自刷新入口命令。取消選定、刷新和自刷新入口命令要求數據輸出管腳為ODT狀態。如圖2所示,通過確認傳輸數據是否帶有讀延遲可以從這些命令中區分出讀命令。 高壓發生器相關文章:高壓發生器原理

評論