基于uSB 2.0接口的高速數據采集系統設計

LJSB(Universal Serial Bus),其中文名稱為"通用串行總線"。他是為了解決計算機外設種類口益增加與有限的主板插槽和端r丁之間的矛盾.由Intel,Microsoft,IBM,NEC,lucent等7家廠商共同制定的總線標準。目前,常用的LISB 2.O版本支持的最高傳輸速度可達到480 Mb/s.他以速度快、成本低、可靠性高、支持即插即用和熱插拔等優點,迅速得到眾多PC廠商的大力支持。同時,開發這種基于uSB 2.0的高速數據采集系統,代表了現代數據采集和傳輸系統的發展趨勢,他也將被越來越多的用戶所接受。

l 系統硬件整體設計

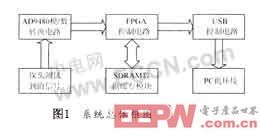

該系統總體框架為PC機(能支持USB 2.O協議的計算機)、A/D轉換模塊、FPGA控制模塊、LYSB控制模塊,如圖l所示。

從整體上看結構可分為2個部分:高速數據采集模塊的設計;USB 2.O高速數據傳輸系統。

1.1數據采集模塊

該系統主要由l片高速AD 芯片、1片SDRAM和l片A1tera公司的FPGA構成。由于系統設計采樣速度最大為1()0 MHz.據采樣定理,采樣頻率至少應在200MHz以上,所以A/D芯片采用Analog公司的高速A/D芯片AD9480。該芯片轉換精度8 b.單一3.3 V電源供電,低功耗,最高工作速度為250 MS/s,采用差分形式、LVDS電平輸出,經過測試可以很好地滿足系統要求。

為了滿足數據采集中高速實時流數據的應用,避免FIFO溢出,本系統通過FPGA及SDRAM構造一個大容量的FIFO,可以提供一個低成本并且能滿足高速實時流數據傳輸的方案。

低速數據采集系統常使用MCU作為CPU來控制,但在高速數據采集系統中,采樣速度往往受MCU速度的影響,而且隨著速度的提高,ADC,SDRAM和MCtJ之間的時序同步問題也顯示出來,因此系統使用了高速FPGA芯片來控制ADC和SDRAM,從而很好地解決了時序精度和同步的問題。

FPGA選擇A1tera公司的CYCLONE系列高性價比產品EPlC6T144C8。他基于1.5 V,O.3 μm及全層銅SRAM工藝,其密度增加至20 060個邏輯元件(LE),RAM增加至288 kb。他具有鎖相環以及DDR SDR和速度周期RAM(FCRAM)存儲器所需的專用雙數據(DDR)接口等。CYCLONE器件支持多種I/O口標準,包括640 Mb/s的LVDS,以及速率為33 MHz和66 MHz,數據寬度為32 b和64 b的PCI。FPGA實現的功能邏輯主要有:實現對ADC的控制,開始A/D轉換;為ADC同步提供SDRAM地址計數和寫信號,把每次A/D轉換的結果直接存入SDRAM,并自動增加地址;當地址計數器達到最大時,發出RAMFULL中斷信號,提示SDRAM已滿。

FPGA的功能邏輯用VHDL語言實現,其編譯和仿真使用Altera公司的QuartusⅡ5.1,使用ByteBlastⅡ并行編程電纜和JTAG口下載編程和配置文件。

1.2 USB 2.0高速數據傳輸

用于USB設備開發的芯片通常有2種類型:一種是MCU集成在芯片里面,如CYPRESS的EZ-USB;另一種是純粹的USB接口芯片,僅處理USB通信,使用時必須由外部微控制器(MCU)進行控制,如Philips的PDIUSBD1 2,National Semiconductor的USBN9604等。在本設計中經過論證分析,采用第一種類型,采用Cypress公司的EZ-USB FX2系列的CY7C68013芯片。

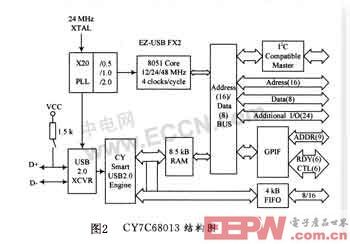

1.2.1 EZ-USB FX2(CY7C68013)芯片

Cypress公司的EZ-USB FX2系列芯片是最早符合USB 2.0協議的微控制器之一,他集成了符合USB 2.O協議的收發器(transceiver),串行接口引擎(SIE),增強型的8051內核以及可編程的外圍接口。FX2系列芯片獨特的結構使得數據傳輸速度最高可達56 Mb/s,最大限度地滿足了USB 2.O的帶寬。CY7C68013集成標準8051內核,且具有下列增強特性:可以達到48 MHz時鐘;每條指令占4個時鐘周期;2個USARTS;3個定時/計數器;擴展的中斷系統;2個數據指針。

805l程序從內部RAM開始運行,借助如下3種方式進行程序裝載:通過USB下載,從E2PROM中裝載;通過外部存儲器設備。內部集成了達4 kB的FIFO,用戶程序發送數據時,直接從FIFO里讀取,保證了數據高速傳輸,與外部實現透明數據傳輸。

1.2.2 硬件連接

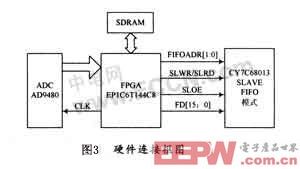

根據系統對數據傳輸的速度和實時性的要求,配置CY7C68013工作的接口模式為Slave FIFO模式。當進行數據采集時,硬件連接方式如圖3所示。

A/D轉換器的采樣時鐘同時作為CY7C68013的Slave F=IFO模式的讀寫控制時鐘,即CY7C68013的接口時鐘連接到IFCLK引腳。SLWR/SLRD是CY7C68013Slave FIFO的寫使能/讀允許信號。FPGA向CY7C268013Slave FIFO提供Slave FIFO輸出允許信號SLOE,僅在數據輸出時有效。FD[15:0]為16 b雙向數據總線。FI-FOADR[1:0]為端點FIFO選擇信號。在數據輸入時固定為OO,選擇端點2;在數據輸出時固定為10,選擇端點6。

2 系統程序設計

USB系統的軟件設計可分為3部分:固件設計、驅動程序設計和用戶端的應用程序設計。

2.1 固件(firmware)設計

固件程序實際上就是單片機方面的軟件設計,他是所有基于微控制器及其外圍電路的功能設備正常工作必不可少的部分,其作用就是輔助硬件。

評論